Pin descriptions – Cypress CY7C1297H User Manual

Page 3

CY7C1297H

Document #: 38-05669 Rev. *B

Page 3 of 15

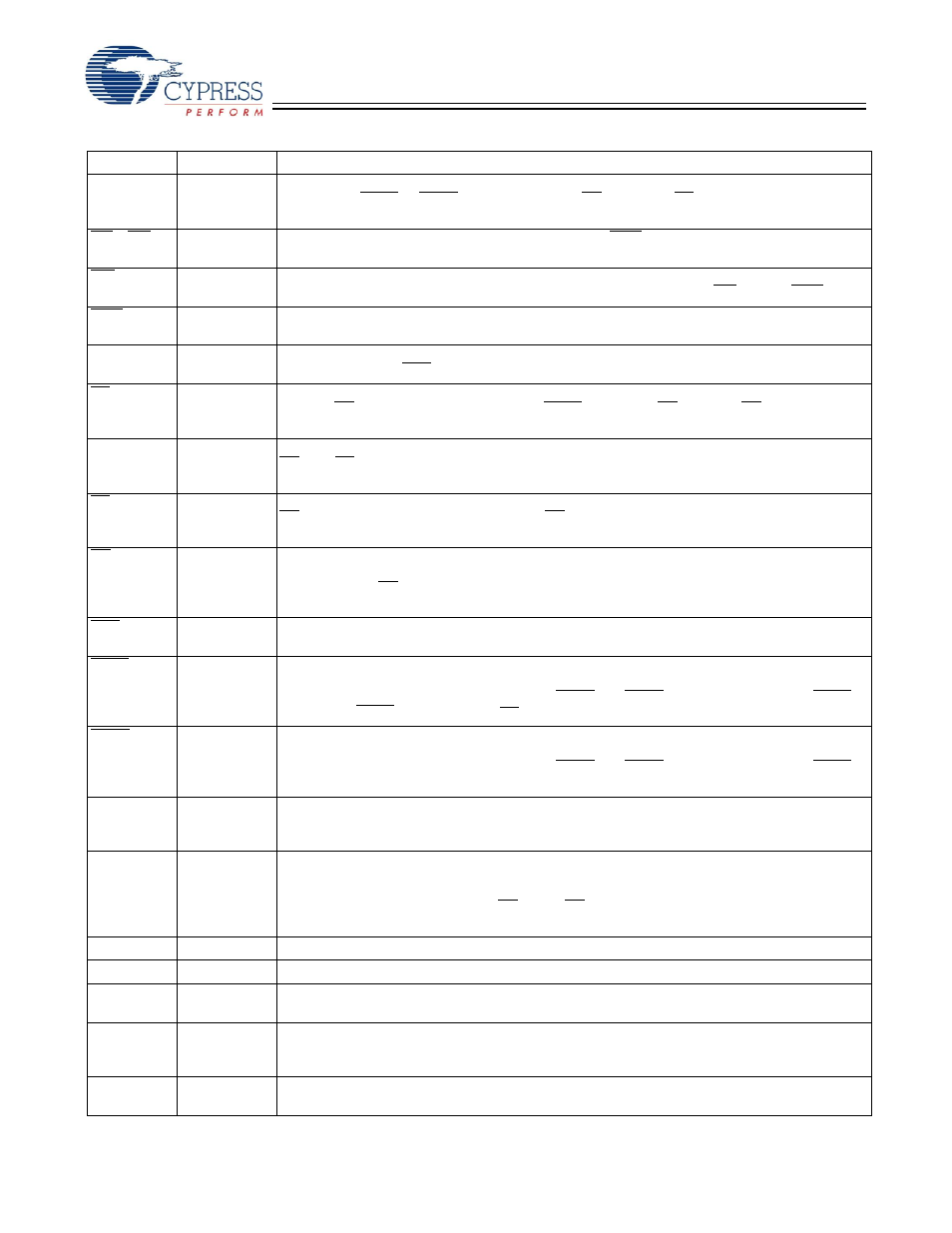

Pin Descriptions

Name

I/O

Description

A0, A1, A

Input-

Synchronous

Address Inputs used to select one of the 64K address locations. Sampled at the rising edge

of the CLK if ADSP or ADSC is active LOW, and CE

1

,

CE

2

, and

CE

3

are sampled active. A

[1:0]

feed the 2-bit counter.

BW

A

, BW

B

Input-

Synchronous

Byte Write Select Inputs, active LOW. Qualified with BWE to conduct Byte Writes to the SRAM.

Sampled on the rising edge of CLK.

GW

Input-

Synchronous

Global Write Enable Input, active LOW. When asserted LOW on the rising edge of CLK, a global

Write is conducted (ALL bytes are written, regardless of the values on BW

[A:B]

and BWE).

BWE

Input-

Synchronous

Byte Write Enable Input, active LOW. Sampled on the rising edge of CLK. This signal must be

asserted LOW to conduct a Byte Write.

CLK

Input-

Clock

Clock Input. Used to capture all synchronous inputs to the device. Also used to increment the

burst counter when ADV is asserted LOW, during a burst operation.

CE

1

Input-

Synchronous

Chip Enable 1 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with

CE

2

and CE

3

to select/deselect the device. ADSP is ignored if CE

1

is HIGH. CE

1

is sampled only

when a new external address is loaded.

CE

2

Input-

Synchronous

Chip Enable 2 Input, active HIGH. Sampled on the rising edge of CLK. Used in conjunction with

CE

1

and CE

3

to select/deselect the device. CE

2

is sampled only when a new external address is

loaded.

CE

3

Input-

Synchronous

Chip Enable 3 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with

CE

1

and CE

2

to select/deselect the device. CE

3

is sampled only when a new external address is

loaded.

OE

Input-

Asynchronous

Output Enable, asynchronous input, active LOW. Controls the direction of the I/O pins. When

LOW, the I/O pins behave as outputs. When deasserted HIGH, I/O pins are tri-stated, and act as

input data pins. OE is masked during the first clock of a Read cycle when emerging from a

deselected state.

ADV

Input-

Synchronous

Advance Input signal, sampled on the rising edge of CLK. When asserted, it automatically

increments the address in a burst cycle.

ADSP

Input-

Synchronous

Address Strobe from Processor, sampled on the rising edge of CLK, active LOW. When

asserted LOW, addresses presented to the device are captured in the address registers. A

[1:0]

are also loaded into the burst counter. When ADSP and ADSC are both asserted, only ADSP is

recognized. ASDP is ignored when CE

1

is deasserted HIGH

ADSC

Input-

Synchronous

Address Strobe from Controller, sampled on the rising edge of CLK, active LOW. When

asserted LOW, addresses presented to the device are captured in the address registers. A

[1:0]

are also loaded into the burst counter. When ADSP and ADSC are both asserted, only ADSP is

recognized.

ZZ

Input-

Asynchronous

ZZ “Sleep” Input, active HIGH. When asserted HIGH places the device in a non-time-critical

“sleep” condition with data integrity preserved. For normal operation, this pin has to be LOW or

left floating. ZZ pin has an internal pull-down.

DQs

DQP

A,

DQP

B

I/O-

Synchronous

Bidirectional Data I/O lines. As inputs, they feed into an on-chip data register that is triggered

by the rising edge of CLK. As outputs, they deliver the data contained in the memory location

specified by the addresses presented during the previous clock rise of the Read cycle. The

direction of the pins is controlled by OE. When OE is asserted LOW, the pins behave as outputs.

When HIGH, DQs and DQP

[A:B]

are placed in a tri-state condition.

V

DD

Power Supply Power supply inputs to the core of the device.

V

SS

Ground

Ground for the device.

V

DDQ

I/O Power

Supply

Power supply for the I/O circuitry.

MODE

Input-

Static

Selects Burst Order. When tied to GND selects linear burst sequence. When tied to V

DD

or left

floating selects interleaved burst sequence. This is a strap pin and should remain static during

device operation. Mode Pin has an internal pull-up.

NC

No Connects. Not Internally connected to the die. 2M, 4M, 9M, 18M, 72M, 144M, 288M, 576M

and 1G are address expansion pins and are not internally connected to the die.