Pci bus overview, 2 pci bus overview – Compaq W4000 User Manual

Page 56

Chapter 4 System Support

4.2

PCI BUS OVERVIEW

NOTE: This section describes the PCI bus in general and highlights bus implementation

in this particular system. For detailed information regarding PCI bus operation, refer to

the PCI Local Bus Specification Revision 2.2.

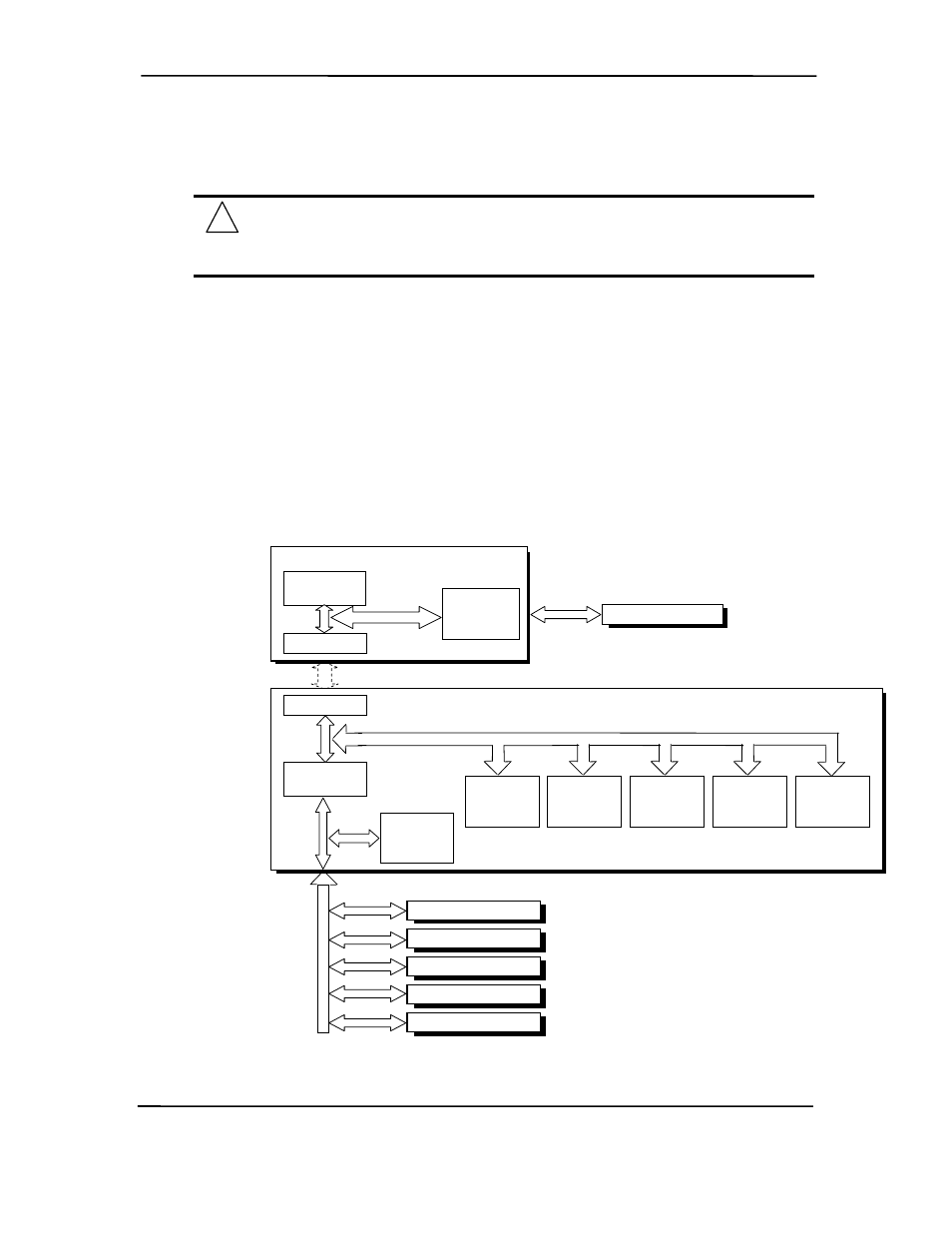

These systems implement a 32-bit Peripheral Component Interconnect (PCI) bus (spec. 2.2)

operating at 33 MHz. The PCI bus handles address/data transfers through the identification of

devices and functions on the bus. A device is typically defined as a component or slot that resides

on the PCI bus (although some components such as the MCH and ICH2 are organized as multip

devices). A function is defined a

le

s the end source or target of the bus transaction. A device may

ontain one or more functions.

he AGP

PCI bus #1. All PCI slots and the NIC function internal to the 82801BA reside on

CI bus #2.

c

In the standard configuration these systems use a hierarchy of three PCI buses (Figure 4-1). The

PCI bus #0 is internal to the 815E chipset components and is not physically accessible. T

bus that services the AGP slot (or resident AGP controller on the Small Form Factor) is

designated as

P

Link Bus

M

omponent

Bridge

Function

Mem. Cntlr.

Function

PCI

Bus #0

.

82801BA ICH2 Component

PCI Br

Func

I/F

Function

Controller

Function

I/F

Function

Controller

Function

Bridge

Function

Audio

Function

PCI Bus #0

AGP Connector

PCI Bus #1

(AGP Bus)

Hub Link I/F

PCI

Bus #2

PCI

Bus #2

PCI Connector 5 [2]

Hub Link

82845 CH C

AGP

I/F

Hub

idge

tion

EIDE

USB

SMBus

LPC

AC97

NIC

PCI Connector 1

PCI Connector 2

PCI Connector 3 [1]

PCI Connector 4 [2]

NOTES:

[1] Desktop and Configurable minitower models only

[2] Configurable minitower models only

Compaq Evo and Workstation Personal Computers

Featuring the Intel Pentium 4 Processor

Second Edition – January 2003

4-2