Research & development, 7 conclusion, 8 faq’s, comments – INFICON Spot CDS550D User Manual

Page 14

Research & Development

SPOT CDS500D & CDS550D OEM Sensor SPI-Interface Specification_V1.1

Page 14 of 14

Christian Berg, T based on Felix Mullis, TL

Created 11/10/2014 2:36:00 PM

5.2.7 Conclusion

The actual sensor configuration results in the following timing parameters:

•

“Total Measurement Cycle”-time (T_tot_cycle)

680µs (+/-15%)

•

“Single Measurement Cycle“-time (T_sgl_cycle)

300µs (+/-15%)

•

“Readout Time Window”-time (T_rd_out)

380µs (+/-15%)

5.2.8 FAQ’s, Comments

Excerpt from an email:

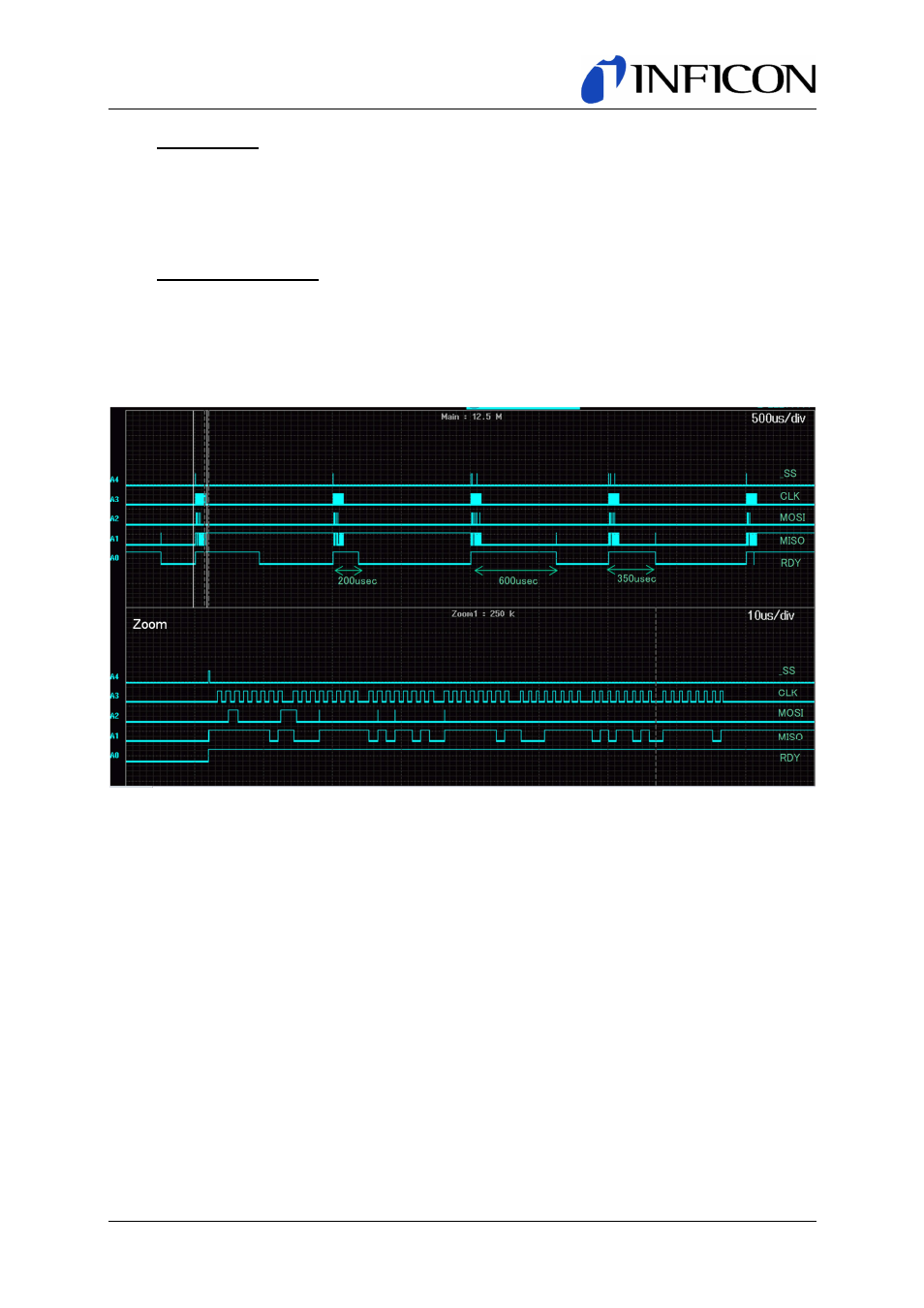

We need to RDY signal example sequence. According to RDY signal shown in the attach-

ment, measuring time is not 500 micro second, some time 200 micro and so on.

Could you give us additional information about RDY.

(See attached file: RDY timing analysis.ppt) below

•

RDY signal is uneven timing

Figure 5: Excerpt from “RDY timing analysis.ppt”

As explained in the chapters above, the overall cycle time is the time between two consecutive nega-

tive going edges of the RDY signal. In the example above, this time equals 710µs and is very stable.

But there is one exception: The 4

th

low going edge of the RDY signal is missing because the readout

of the actual value was too late, or in other words, the next measurement cycle has started before the

Host was able to read the actual value.

The reason for the observed timing behavior of the RDY signal is the ignoring of the timing specifica-

tions.