Research & development – INFICON Spot CDS550D User Manual

Page 12

Research & Development

SPOT CDS500D & CDS550D OEM Sensor SPI-Interface Specification_V1.1

Page 12 of 14

Christian Berg, T based on Felix Mullis, TL

Created 11/10/2014 2:36:00 PM

5.2.3 Total Measurement Cycle

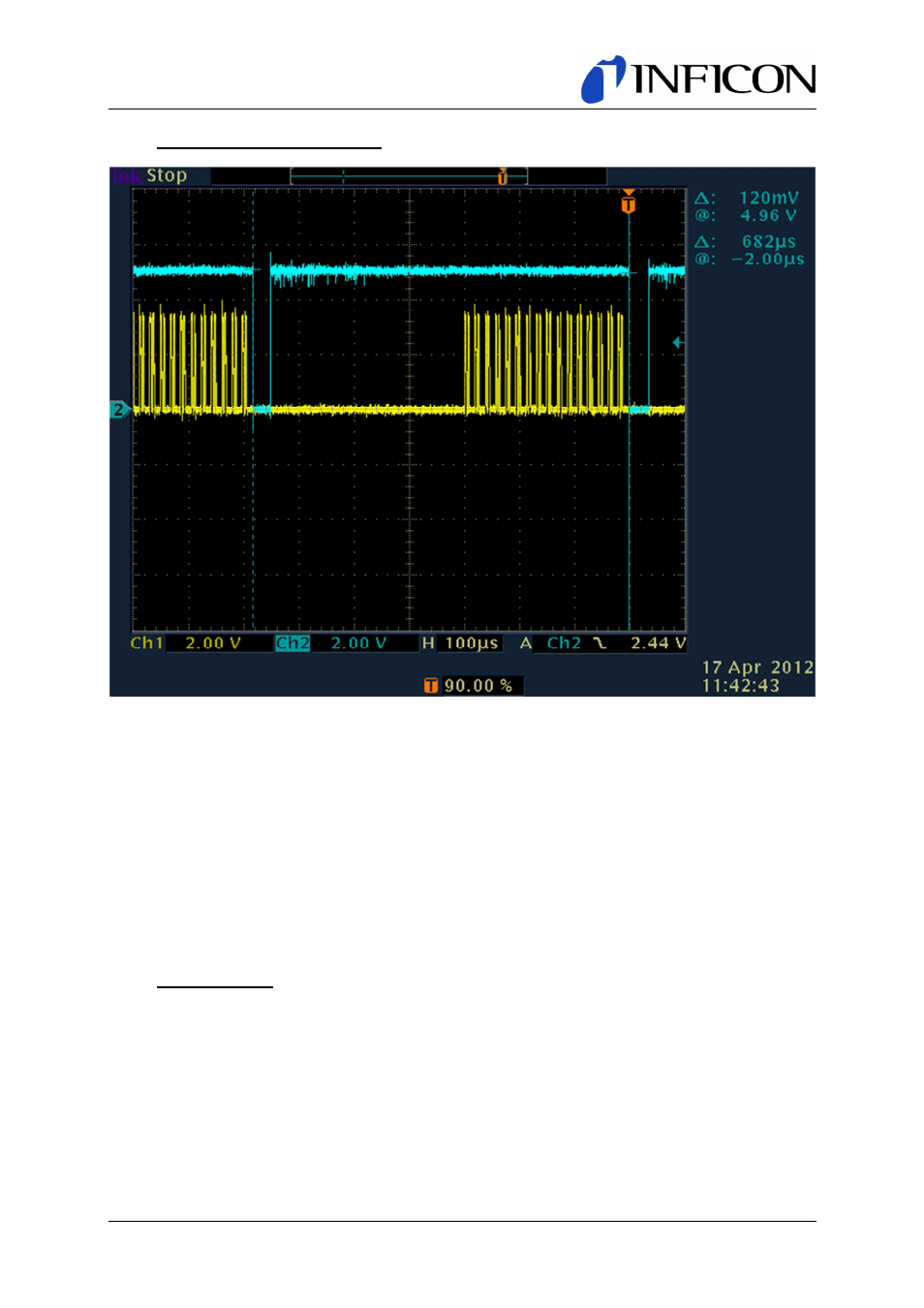

Figure 3: Measurement Cycle

•

Ch 1 (yellow) depicts the signal directly at the sensor

•

Ch 2 (blue) equals the RDY (Ready) signal

Figure 3 shows a measurement cycle. A measurement cycle is defined as the time between two con-

secutive negative edges of the Ready-signal. As can be seen from Figure 3, that time equals 682µs.

The timing source for the measurement cycle is an on chip oscillator. Although it is very stable it

shows a relatively large absolute frequency tolerance of about +/- 15% from chip to chip. Therefore the

cycle time can also vary in the range of about +/-15% from sensor to sensor.

5.2.4 Ready-signal

The Ready-signal is active low and it is set after the first measurement value is available. The Ready-

signal is reset by assigning the SS/-signal active. (SPI Slave Select) that means it is automatically

reset by a consecutive read of the measurement value.