Serial port, Figure 1, Figure 2 illustrates the i – Cirrus Logic CS5529 User Manual

Page 11: Khz, see figure 2), Cs5529, Φ fine, V≤ 25mv i = fv c, Φ coarse

CS5529

DS246F5

11

ages. The differential voltage between VREF+ and

VREF- sets the nominal full scale input span of the

converter. For a single-ended reference voltage,

such as the LT1019-2.5, the reference output is

connected to the VREF+ pin of the CS5529 and the

ground reference for the LT1019-2.5 is connected

to the VREF- pin.

Serial Port

The CS5529 includes a microcontroller with a

command register, a configuration register, a con-

version data register (read only), and a gain and off-

set register for calibration. All registers, except the

8-bit command register, are 24-bits in length. Fig-

ure 3 illustrates a block diagram of all the internal

register.

After a system initialization or reset, the serial port

is set to the command mode. The converter stays in

this mode until a valid 8-bit command is received

(the first 8-bits into the serial port). Once a valid 8-

bit command is received and interpreted by the

ADC’s command register, the serial port enters the

data mode. In data mode the next 24 serial clock

pulses shift data either into or out of the serial port

(72 serial clock pulses are needed if the setup reg-

ister command is issued). The Command Register

Descriptions section illustrates all valid com-

mands.

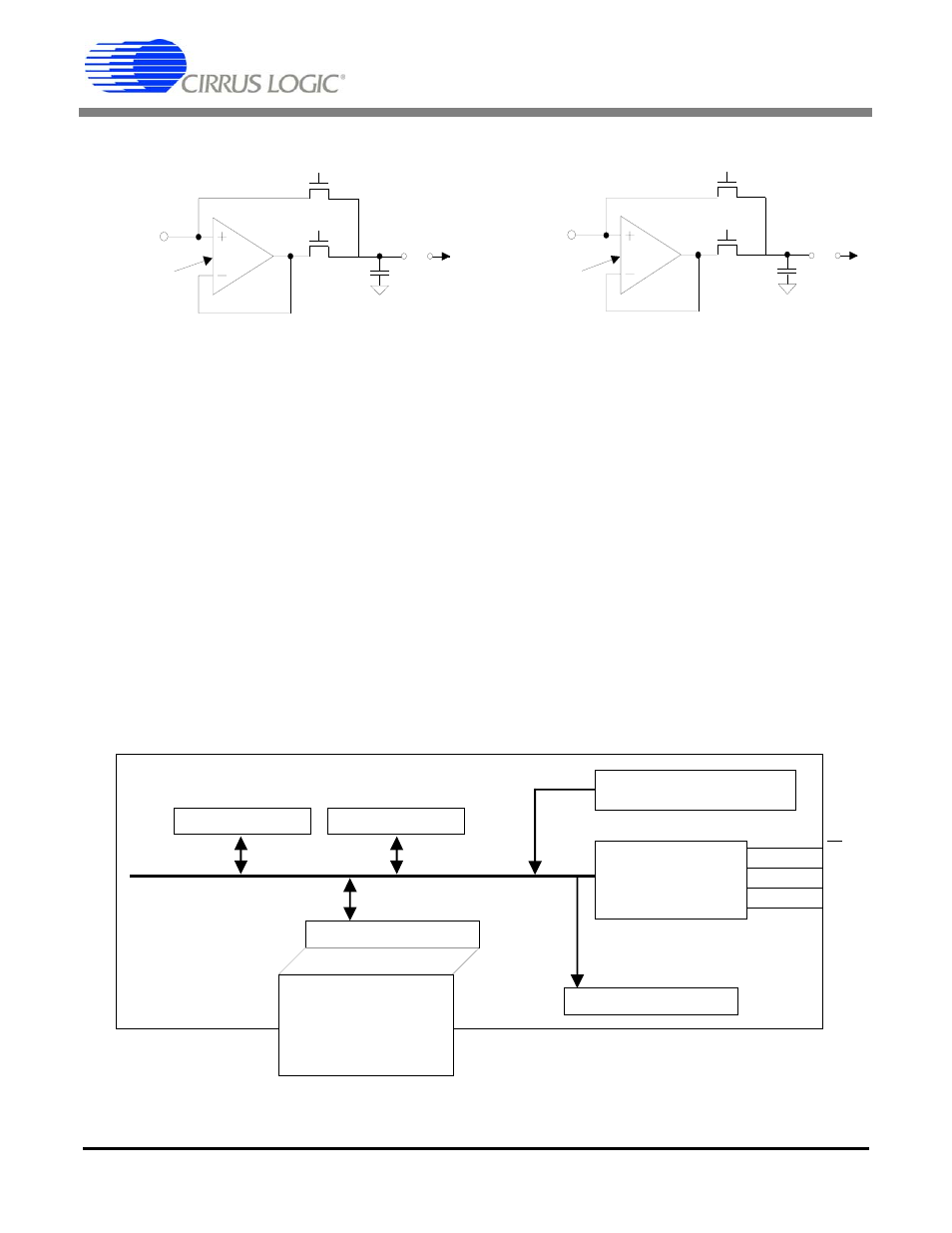

AIN

C = 20pF

f = 32.768 kHz

φ Coarse

1

φ Fine

1

V

≤ 25mV

i = fV C

os

os

n

Figure 1. Input models for AIN+ and AIN- pins.

VREF

C = 10pF

f = 32.768 kHz

2

φ Fine

1

V

≤ 25mV

i = fV C

os

os

n

φ Coarse

Figure 2. Input model for VREF+ and VREF- pins.

Latch Outputs

Low Power Mode

Output Word Rates

Unipolar/Bipolar

Reset System

etc.

Configuration Register (1 × 24)

Serial

Interface

CS

SDI

SDO

SCLK

Command Register (1 × 8)

Wr

it

e

O

n

ly

Re

a

d

O

n

ly

Conversion Data Register (1x24)

Gain Register (1 × 24)

Offset Register (1 × 24)

Figure 3. CS5529 Register Diagram.