Cdb5374 – Cirrus Logic CDB5374 User Manual

Page 27

CDB5374

DS862DB1

27

input on CDB5374 can receive a lower-frequency system clock and create a synchronous higher-frequen-

cy clock using an on-board PLL.

The expected input clock frequency to the BNC clock input is set by the EXT_CLK jumper (J16). If no ex-

ternal clock is supplied to CDB5374, the PLL will free-run at the nominal output frequency.

The PLL on CDB5374 uses a voltage-controlled crystal oscillator (VCXO) to minimize jitter, and has a sin-

gle-gate phase/frequency detector and clock divider to minimize size and power.

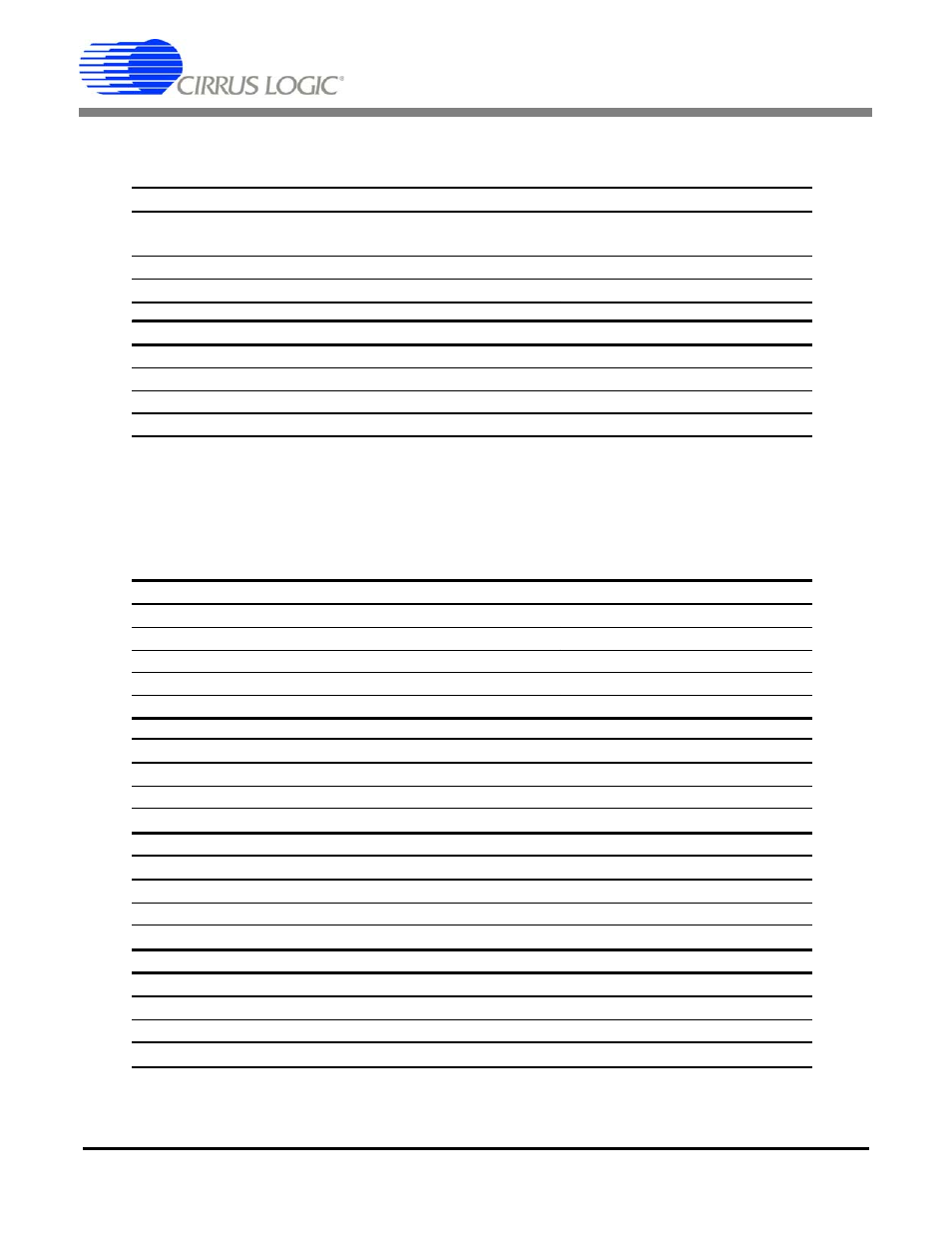

Specification Value

Input Clock Frequency

1.024, 2.048, 4.096 MHz

8.192, 16.384, 32.768 MHz

Distributed Clock Synchronization

± 240 ns

Maximum Input Clock Jitter, RMS

1 ns

Specification Value

PLL Output Clock Frequency

32.768 MHz

Maximum Output Jitter, RMS

300 ps

Oscillator Type

VCXO

Detector Architecture

Phase / Frequency

Specification Value

Oscillator - Citizen 32.768 MHz VCXO

CSX750VBEL32.768MTR

Surface Mount Package Type

Leadless 6-Pin, 5x7 mm

Supply Voltage, Current

3.3 V, 11 mA

Frequency Stability, Pullability

± 50 ppm, ± 90 ppm

Startup Time

4 ms

Specification Value

Phase Detector - TI LittleLogic XOR

SN74LVC1G86DBVR

Surface Mount Package Type

SOT23-5

Supply Voltage, Current

3.3 V, 10

µA

Specification Value

Loop Filter Integrator - Linear Tech Op-Amp

LT1783IS5

Surface Mount Package Type

SOT23-5

Supply Voltage, Current

3.3 V, 375

µA

Specification Value

Clock Divider - TI LittleLogic D-Flop

SN74LVC2G74DCTR

Surface Mount Package Type

SSOP8-199

Supply Voltage, Current

3.3 V, 10

µA