Cirrus Logic CS5340 User Manual

Cs5340, Features, General description

Copyright

© Cirrus Logic, Inc. 2008

(All Rights Reserved)

101 dB, 192 kHz, Multi-Bit Audio A/D Converter

Features

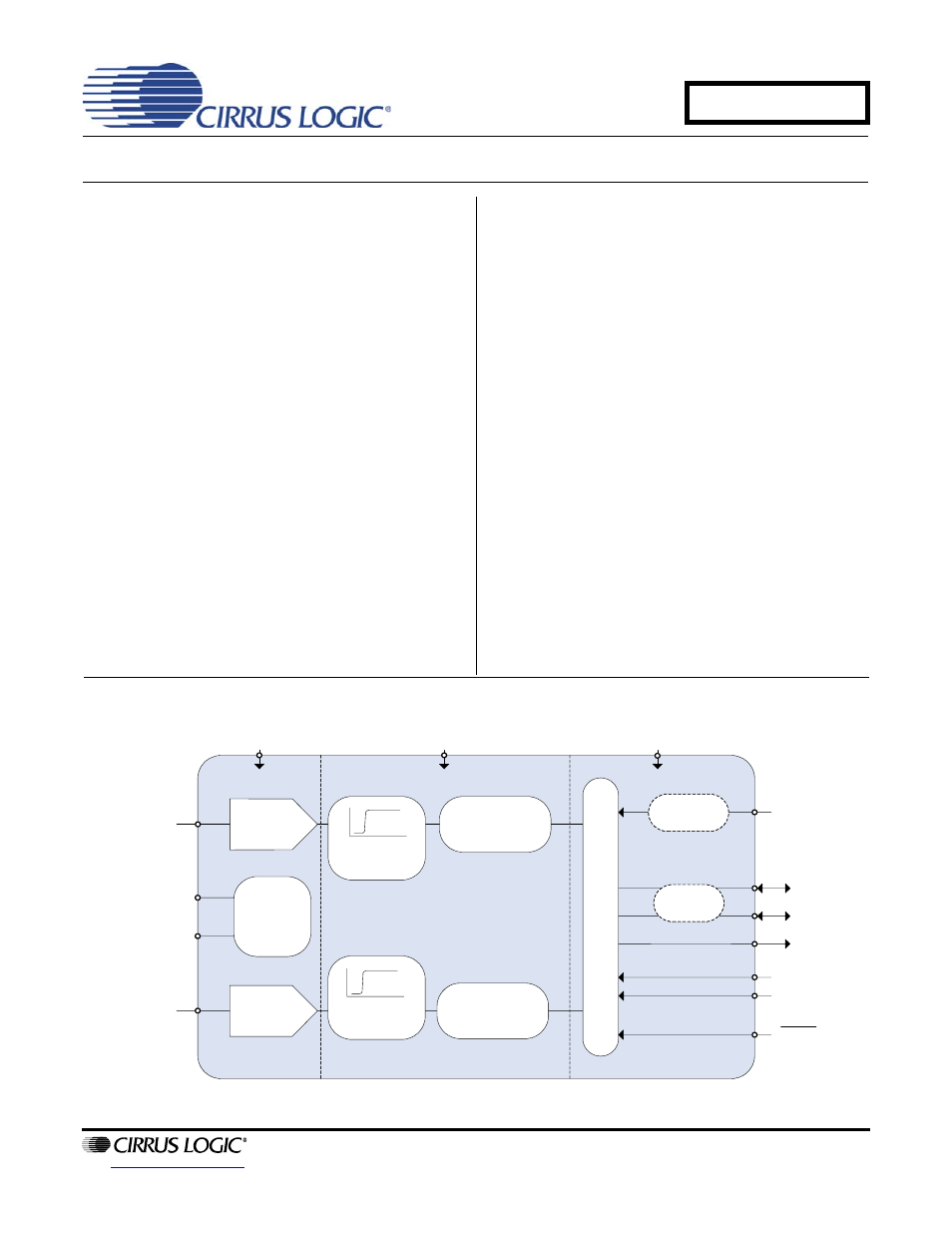

Advanced Multi-bit Delta-Sigma Architecture

24-bit Conversion

Supports All Audio Sample Rates Including

192 kHz

101 dB Dynamic Range at 5 V

-94 dB THD+N

90 mW Power Consumption

High-Pass Filter to Remove DC Offsets

Analog/Digital Core Supplies from 3.3 V to 5 V

Supports Logic Levels between 1.8 V and 5 V

Auto-detect Mode Selection in Slave Mode

Auto-Detect MCLK Divider

Pin Compatible with CS5341

General Description

The CS5340 is a complete analog-to-digital converter

for digital audio systems. It performs sampling, analog-

to-digital conversion, and anti-alias filtering, generating

24-bit values for both left and right inputs in serial form

at sample rates up to 200 kHz per channel.

The CS5340 uses a 5th-order, multi-bit Delta-Sigma

modulator followed by digital filtering and decimation,

which removes the need for an external anti-alias filter.

The CS5340 is available in a 16-pin TSSOP package

for Commercial (-10° to +70° C) and Automotive grades

(-40° to +85° C). The CDB5340 Customer Demonstra-

tion Board is also available for device evaluation and

implementation suggestions. Please refer to

for complete ordering

information.

The CS5340 is ideal for audio systems requiring wide

dynamic range, negligible distortion and low noise, such

as set-top boxes, DVD-karaoke players, DVD record-

ers, A/V receivers, and automotive applications.

High-Pass

Filter

Low-Latency

Digital Filters

High-Pass

Filter

Se

ri

al

P

o

rt

VA

3.3 V to 5 V

Internal

Reference

Voltages

Switch-Cap

ADC

VD

3.3 V to 5 V

VL

1.8 V to 5 V

Auto-detect

MCLK Divider

Slave Mode

Auto-detect

Master Clock

Reset

Single-Ended

Analog Input

Low-Latency

Digital Filters

Switch-Cap

ADC

Mode

Configuration

Single-Ended

Analog Input

SCLK

LRCK

SDOUT

M0

M1

FILT+

VQ

AINR

AINL

March '08

DS601F2

Confidential Draft

3/11/08

CS5340

Document Outline

- Table of Contents

- List of Figures

- List of Tables

- 1. Characteristics and Specifications

- Specified Operating Conditions

- Absolute Maximum Ratings

- Analog Characteristics - Commercial Grade

- Analog Characteristics - Automotive Grade

- Digital Filter Characteristics

- Figure 1. Single-Speed Mode Stopband Rejection

- Figure 2. Single-Speed Mode Stopband Rejection

- Figure 3. Single-Speed Mode Transition Band (Detail)

- Figure 4. Single-Speed Mode Passband Ripple

- Figure 5. Double-Speed Mode Stopband Rejection

- Figure 6. Double-Speed Mode Stopband Rejection

- Figure 7. Double-Speed Mode Transition Band (Detail)

- Figure 8. Double-Speed Mode Passband Ripple

- Figure 9. Quad-Speed Mode Stopband Rejection

- Figure 10. Quad-Speed Mode Stopband Rejection

- Figure 11. Quad-Speed Mode Transition Band (Detail)

- Figure 12. Quad-Speed Mode Passband Ripple

- DC Electrical Characteristics

- Digital Characteristics

- Switching Characteristics - Serial Audio Port

- 2. Pin Description

- 3. Typical Connection Diagram

- Figure 17. Typical Connection Diagram

- 4. Applications

- 5. Parameter Definitions

- 6. Package Dimensions

- 7. Ordering Information

- 8. Revision History