Cirrus Logic CDB48500-USB User Manual

Page 22

8

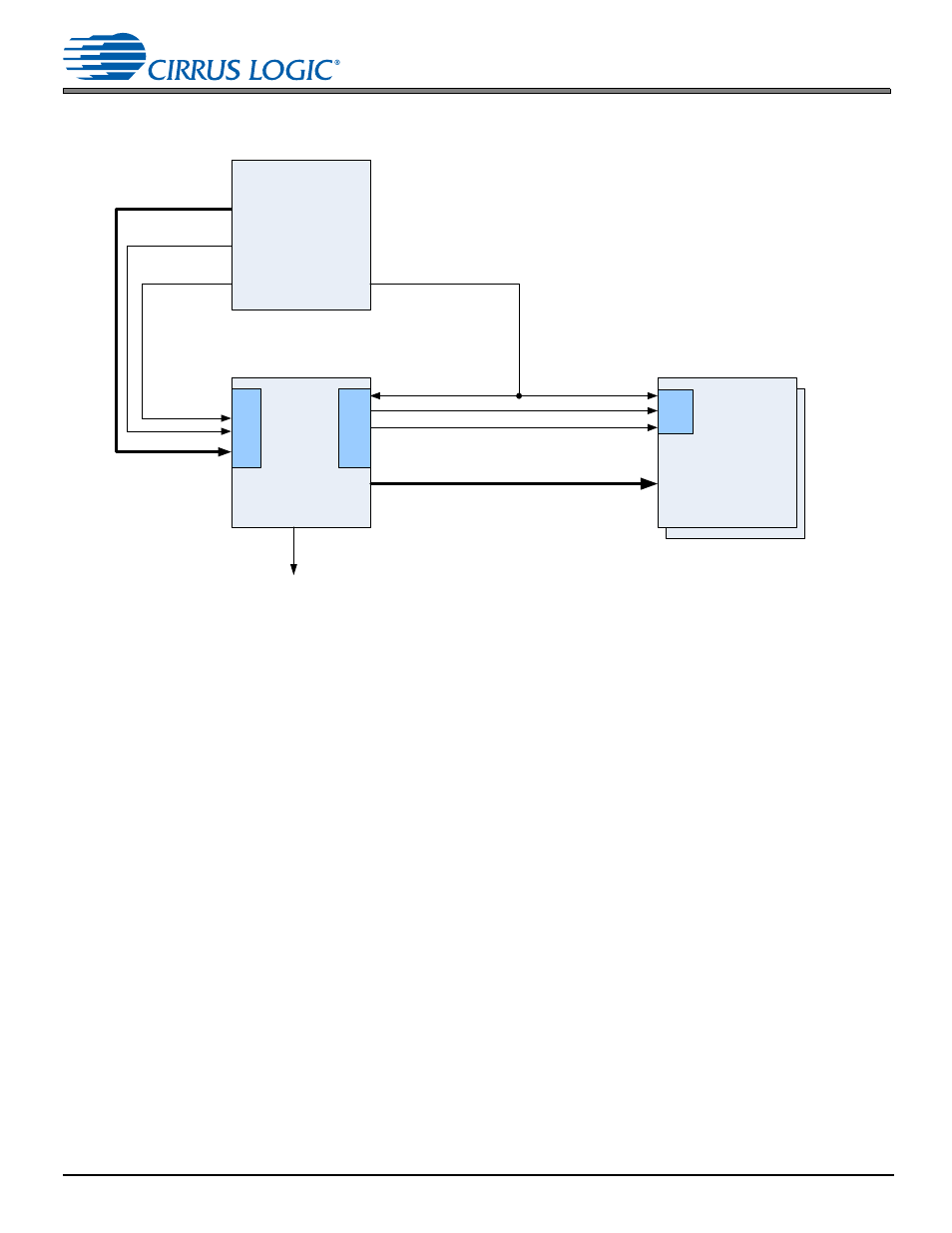

3.1.11.3 Clock and Data Flow for CDB USB Master Card Source

Figure 3-4. CDB USB Master Card Clocking and Data Flow

illustrates the clocking architecture used when IIS(USB) is used as an audio source, as described in

Section 4.2.2, “Changing the Audio Input Source” on page 4-3

). MCLK is generated by the PLL on the USB

Master card. The PLD on the USB Master Card generates SCLK and LRCLK for the DAI side of the DSP from

the MCLK.

On the output side, the CS485xx slaves to MCLK from the USB Master Card and masters SCLK and LRCLK for

the DAC side of the CS42448.The CS485XX always masters its output clocks (DSP_SCLK/DSP_LRCLK).

§§

CS42448

2x

CS485XX

CS42448

2x

CDB USB

MASTER

CARD

MUXED_DSP_SCLK1

DSP_SCLK

DSP_LRCLK

MUXED_DSP_LRCLK1

MUXED_DAI[4:0]

DSP_DA01[3:0]

XMTA SPDIF OUT

MUXED_MCLK

DAI

DAO

SDIN

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)