Cirrus Logic CS4396 User Manual

Advance product information, Features, Description

Table of contents

Document Outline

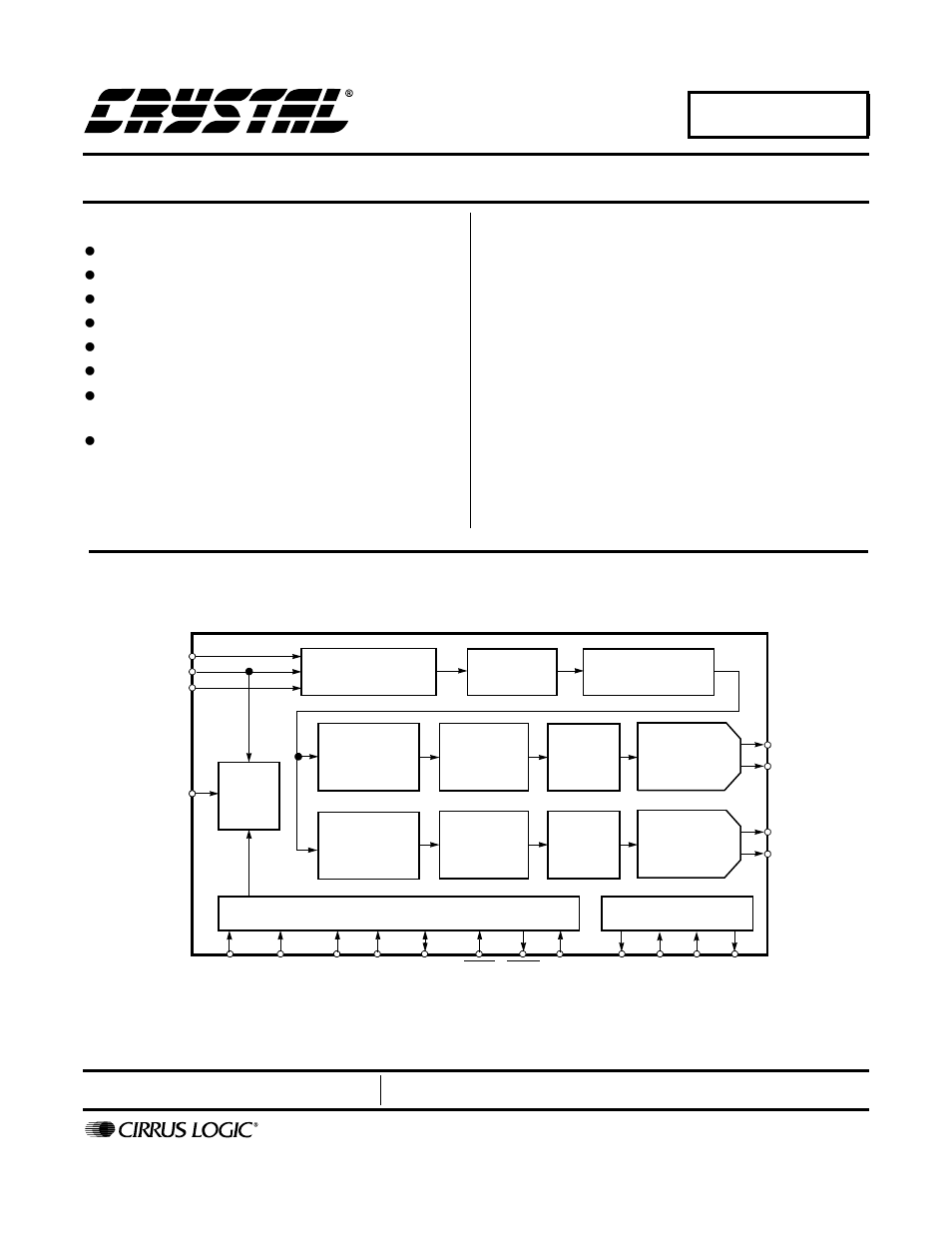

- CS4396

- Features

- Description

- Table of Contents

- Table of Figures

- 1.0 Characteristics/Specifications

- 2.0 Typical Connection Diagram

- 3.0 Register Description

- 4.0 PIN DESCRIPTION

- Pin Description Drawing

- Table 4. Single Speed (16 to 50 kHz sample rates) Common Clock Frequencies

- Table 5. Double Speed (50 to 100 kHz sample rates) Common Clock Frequencies

- Table 6. Quad Speed (100 to 200 kHz sample rates) Common Clock Frequencies

- Reset - RST

- Digital Ground - DGND

- Digital Power - VD

- Master Clock - MCLK

- Serial Clock - SCLK

- Left/Right Clock - LRCK

- Serial Audio Data - SDATA

- Soft Mute - MUTE

- Control Port / Hardware Mode Select - C/H

- Mute Control - MUTEC

- Analog Ground - AGND

- Differential Analog Outpus - AOUTR- , AOUTR+ and AOUTL- , AOUTL+

- Analog Power - VA

- Common Mode Voltage - CMOUT

- Reference Ground - FILT-

- Reference Filter - FILT+

- Voltage Reference Input- VREF

- HARDWARE MODE

- CONTROL PORT MODE

- 5.0 APPLICATIONS

- 6.0 Control Port Interface

- 6.1 SPI Mode

- 6.2 I2C Mode

- Memory Address Pointer (MAP)

- Figure 5. Control Port Timing, SPI mode

- Figure 6. Control Port Timing, I2C Mode

- Table 7. Single Speed (16 to 50kHz) Digital Interface Format Options

- Table 8. Single Speed (16 to 50kHz) De-Emphasis Options

- Table 9. Double Speed (50 to 100 kHz) Sample Rate Mode Options

- Table 10. Quad (100 to 200 kHz) Sample Rate Mode Options

- Figure 7. Single-speed Transition Band

- Figure 8. Single-speed Stopband Rejection

- Figure 9. Single-speed Transition Band

- Figure 10. Single-speed Frequency Response

- Figure 11. Double-speed Stopband

- Figure 12. Double-speed Transition Band

- Figure 13. Double-speed Transition Band

- Figure 14. Double-speed Frequency Response

- Figure 15. Quad-speed Stopband Rejection

- Figure 16. Quad-speed Transition Band

- Figure 17. Quad-speed Transition Band

- Figure 18. Quad-speed Frequency Response

- Figure 19. De-Emphasis Curve

- Figure 20. Format 0, Left Justified

- Figure 21. Format 1, I2S

- Figure 22. Format 2, Right Justified, 16-Bit Data

- Figure 23. Format 3, Right Justified, 24-Bit Data

- Memory Address Pointer (MAP)

- 7.0 PARAMETER DEFINITIONS

- 8.0 REFERENCES

- 9.0 PACKAGE DIMENSIONS