0 pin description, Pin description drawing, Reset - rst – Cirrus Logic CS4396 User Manual

Page 14: Digital ground - dgnd, Digital power - vd, Master clock - mclk, Cs4396

CS4396

14

DS288PP1

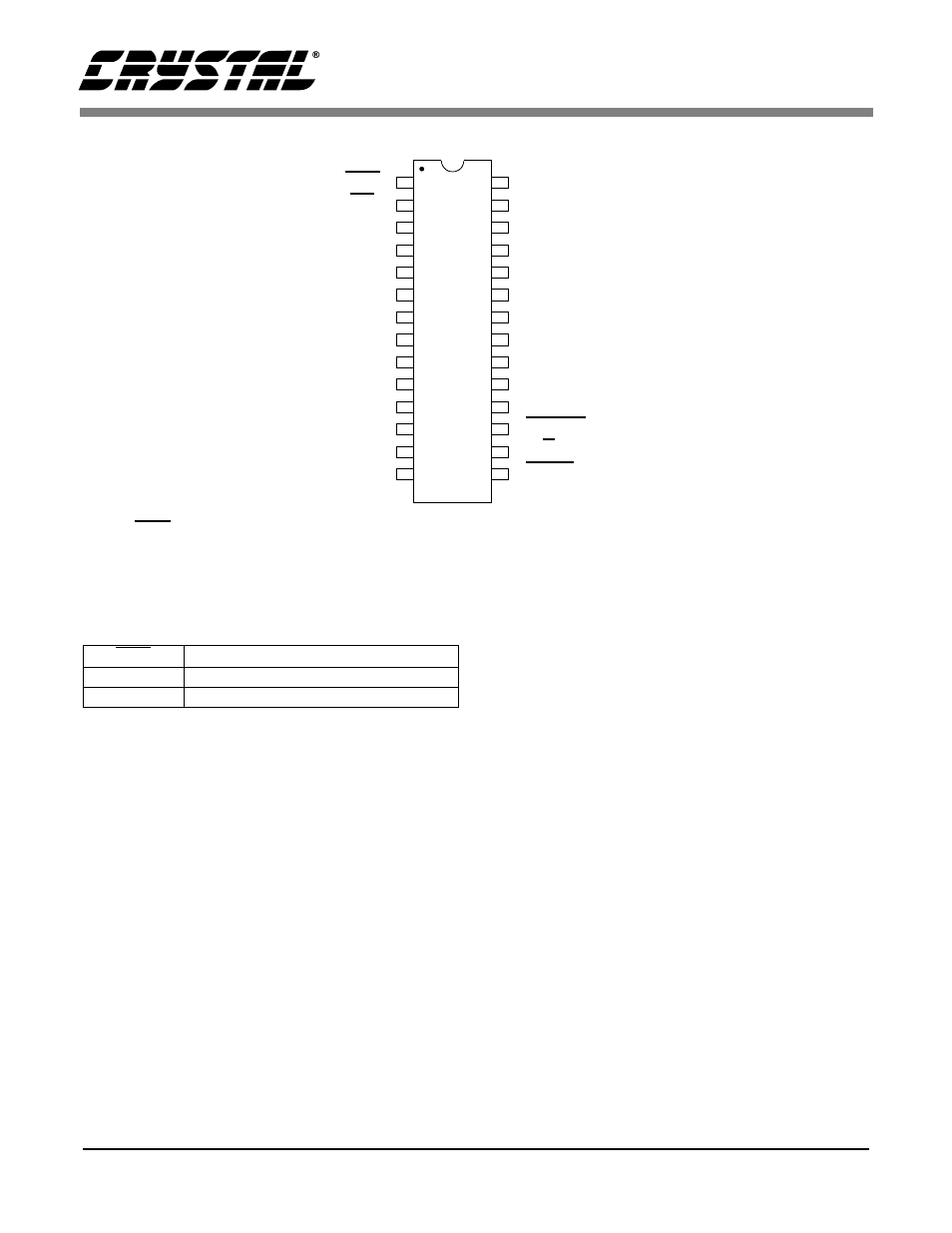

4.0 PIN DESCRIPTION

Reset - RST

Pin 1, Input

Function:

The device enters a low power mode and all internal state machines registers are reset when low. When

high, the device will be in a normal operation mode .

Digital Ground - DGND

Pins 6 and 9, Inputs

Function:

Digital ground reference.

Digital Power - VD

Pins 7 and 8, Input

Function:

Digital power supply. Typically 5.0 to 3.0 VDC.

Master Clock - MCLK

Pin 10, Input

Function:

The master clock frequency must be either 256x, 384x, 512x or 768x the input sample rate in Single

Speed Mode; either 128x, 192x 256x or 384x the input sample rate in Double Speed Mode; or 64x, 96x

128x or 192x the input sample rate in Quad Speed Mode. Tables 4-6 illustrate the standard audio sample

rates and the required master clock frequencies.

RST

DESCRIPTION

0

Enabled

1

Normal operation mode

1

2

3

4

5

6

7

8

9

10

11

12

5

1

2

6

28

27

26

25

24

23

22

21

20

19

18

17

13

14

16

15

Reset

RST

VREF

Voltage Reference

See Description

M4(AD0/CS)

FILT+

Reference Filter

See Description

M3(AD1/CDIN)

FILT-

Reference Ground

See Description

M2(SCL/CCLK)

CMOUT

Common ModeS Voltage

See Description M0(SDA/CDOUT)

AOUTL-

Differential Output

Digital Ground

DGND

AOUTL+

Differential Output

Digital Power

VD

VA

Analog Power

Digital Power

VD

AGND

Analog Ground

Digital Ground

DGND

AOUTR+

Differential Output

Master Clock

MCLK

AOUTR-

Differential Output

Serial Clock

SCLK

AGND

Analog Ground

Left/Right Clock

LRCK

MUTEC

Mute Control

Serial Data

SDATA

C/H

Control port/Hardware select

See Description

M1

MUTE

Soft Mute