Pin description, Cs4364, Pin name # pin description – Cirrus Logic CS4364 User Manual

Page 6

6

DS619F1

CS4364

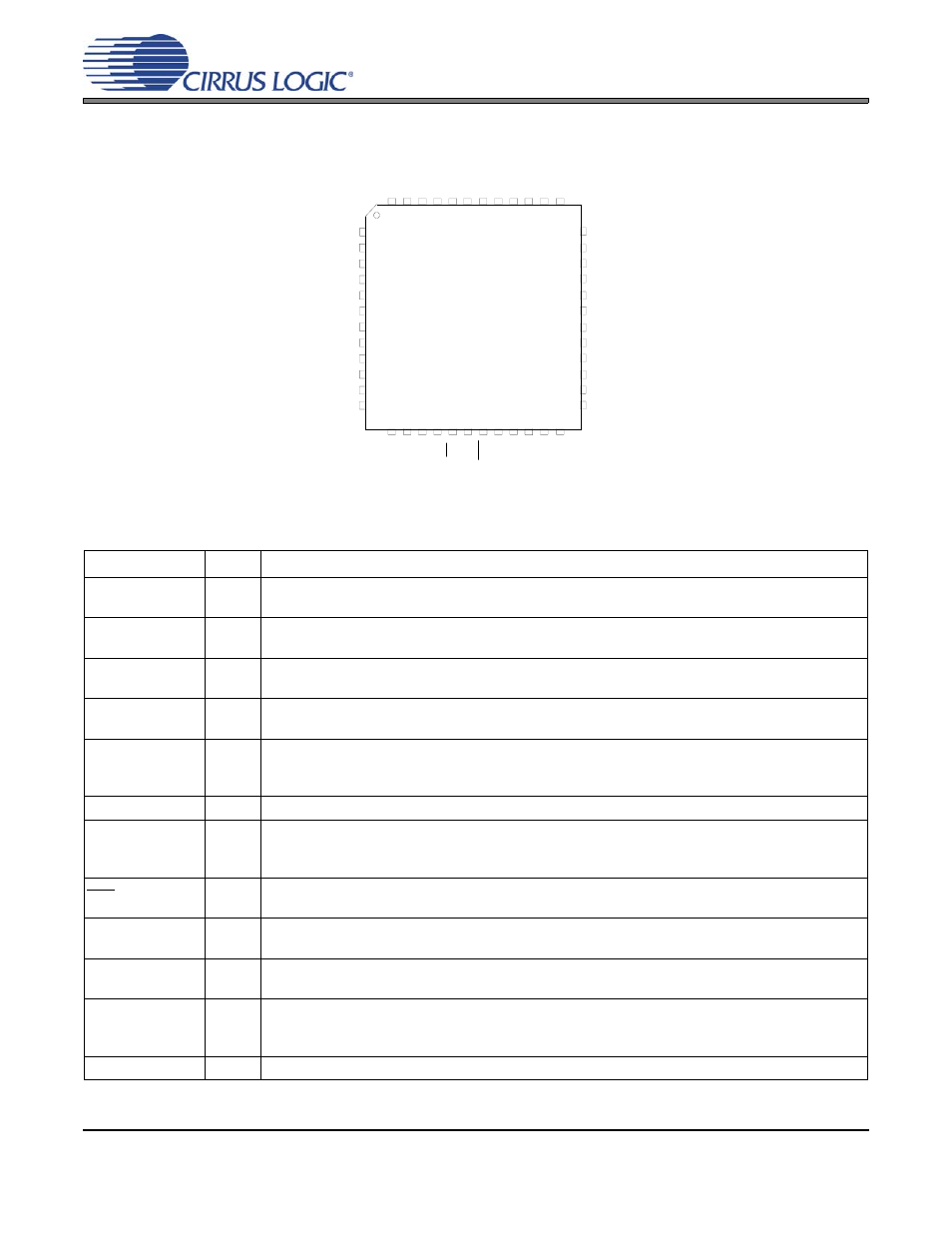

1. PIN DESCRIPTION

Pin Name

#

Pin Description

VD

4

Digital Power (Input) - Positive power supply for the digital section. Refer to the Recommended

Operating Conditions for appropriate voltages.

GND

5

31

Ground (Input) - Ground reference. Should be connected to analog ground.

MCLK

6

Master Clock (Input) - Clock source for the delta-sigma modulator and digital filters.

illus-

trates several standard audio sample rates and the required master clock frequencies.

LRCK

7

Left Right Clock (Input) - Determines which channel, Left or Right, is currently active on the

serial audio data line. The frequency of the left/right clock must be at the audio sample rate, Fs.

SDIN1

SDIN2

SDIN3

8

11

13

Serial Data Input (Input) - Input for two’s complement serial audio data.

SCLK

9

Serial Clock (Input) - Serial clocks for the serial audio interface.

TST

14

44

45

Test - These pins need to be tied to analog ground.

RST

19

Reset (Input) - The device enters a low power mode and all internal registers are reset to their

default settings when low.

VA

32

Analog Power (Input) - Positive power supply for the analog section. Refer to the Recommended

Operating Conditions for appropriate voltages.

VLS

43

Serial Audio Interface Power (Input) - Determines the required signal level for the serial audio

interface. Refer to the Recommended Operating Conditions for appropriate voltages.

VLC

18

Control Port Power (Input) - Determines the required signal level for the control port and hard-

ware mode configuration pins. Refer to the Recommended Operating Conditions for appropriate

voltages.

VQ

21

Quiescent Voltage (Output) - Filter connection for internal quiescent voltage.

SD

IN

3

GND

TST_OUT

AOUT5

TST_OUT

AOUT4

VA

TST_OUT

AOUT6

MUTE2

MUTE3

6

2

4

8

10

1

3

5

7

9

11

12

13 14 15 16 17 18 19 20 21 22 23 24

31

35

33

29

27

36

34

32

30

28

26

25

48 47 46 45 44 43 42 41 40 39 38 37

MCLK

DSD2

VD

SDIN1

M4(TST)

DSD3

DSD1

GND

SCLK

SDIN2

M3(TST)

LRCK

DS

D_SC

L

K

DSD

6

DSD

5

TS

T

CS4364

TS

T

VLS

TS

T

M2(S

CL/C

CLK)

M1

(SDA

/C

DIN

)

VL

C

RS

T

FI

L

T

+

VQ

MUT

E

6

MUT

E

5

MUT

E

4

M0(

A

D0/

C

S)

AOUT3

TST_OUT

AO

UT2

TS

T

_

O

U

T

TS

T_OU

T

AOU

T

1

DS

D

4

MUT

E

1