Figure 4. control port timing - i·c format, Figure 4. control port timing - i²c format – Cirrus Logic CS4364 User Manual

Page 16

16

DS619F1

CS4364

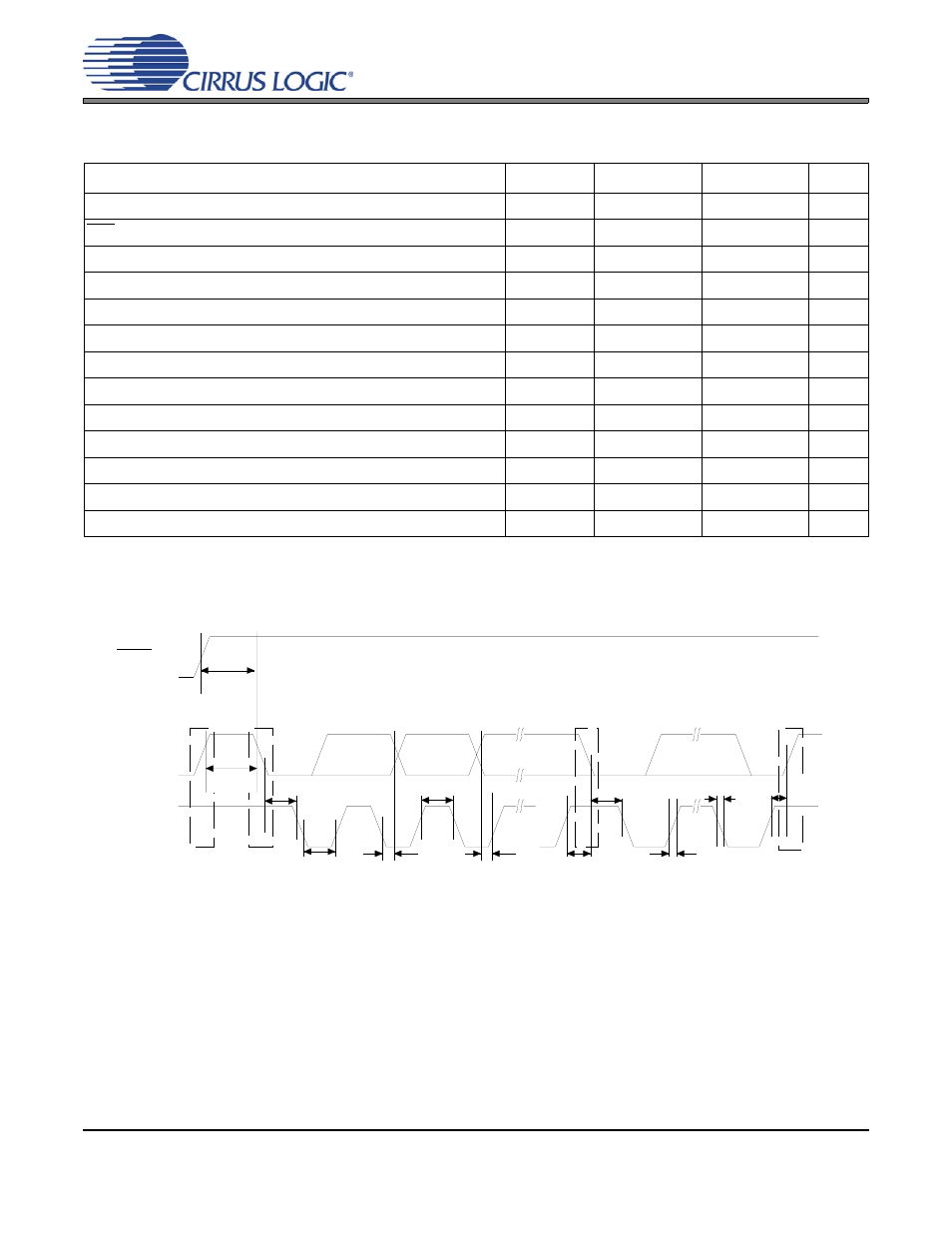

SWITCHING CHARACTERISTICS - CONTROL PORT - I²C FORMAT

(Inputs: Logic 0 = GND, Logic 1 = VLC, C

L

= 30 pF)

Notes:

16. Data must be held for sufficient time to bridge the transition time, t

fc

, of SCL.

Parameter

Symbol

Min

Max

Unit

SCL Clock Frequency

f

scl

-

100

kHz

RST Rising Edge to Start

t

irs

500

-

ns

Bus Free Time Between Transmissions

t

buf

4.7

-

µs

Start Condition Hold Time (prior to first clock pulse)

t

hdst

4.0

-

µs

Clock Low time

t

low

4.7

-

µs

Clock High Time

t

high

4.0

-

µs

Setup Time for Repeated Start Condition

t

sust

4.7

-

µs

SDA Hold Time from SCL Falling

t

hdd

0

-

µs

SDA Setup time to SCL Rising

t

sud

250

-

ns

Rise Time of SCL and SDA

t

rc

, t

rc

-

1

µs

Fall Time SCL and SDA

t

fc

, t

fc

-

300

ns

Setup Time for Stop Condition

t

susp

4.7

-

µs

Acknowledge Delay from SCL Falling

t

ack

300

1000

ns

t

buf

t

hdst

t

hdst

t

lo w

t r

t f

t

hdd

t

high

t sud

t sust

t susp

Stop

S ta rt

S ta rt

Stop

R e p e a te d

S D A

S C L

t

irs

R S T

Figure 4. Control Port Timing - I²C Format

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)