Applications, 1 sample rate range/operational mode detect, 1 auto-detect enabled – Cirrus Logic CS4351 User Manual

Page 15: Table 1. cs4351 auto-detect, 2 auto-detect disabled, Table 2. cs4351 mode select, 2 system clocking, 1 auto-detect enabled 4.1.2 auto-detect disabled

DS566F1

15

CS4351

4. APPLICATIONS

4.1

Sample Rate Range/Operational Mode Detect

The device operates in one of three operational modes. The allowed sample rate range in each mode will

depend on whether the Auto-Detect Defeat bit is enabled/disabled.

4.1.1

Auto-Detect Enabled

The Auto-Detect feature is enabled by default. In this state, the CS4351 will auto-detect the correct mode

when the input sample rate (F

s

), defined by the LRCK frequency, falls within one of the ranges illustrated

. Sample rates outside the specified range for each mode are not supported.

4.1.2

Auto-Detect Disabled

The Auto-Detect feature can be defeated only by the format bits in the control port register 02h. In this

state, the CS4351 will not auto-detect the correct mode based on the input sample rate (F

s

). The opera-

tional mode must then be set manually according to one of the ranges illustrated in

. Please refer

to

for implementation details. Sample rates outside the specified range for each mode are

not supported. In stand-alone mode it is not possible to disable auto-detect of sample rates.

4.2

System Clocking

The device requires external generation of the master (MCLK), left/right (LRCK) and serial (SCLK) clocks.

The left/right clock, defined also as the input sample rate (F

s

), must be synchronously derived from the

MCLK according to specified ratios. The specified ratios of MCLK to LRCK, along with several standard au-

dio sample rates and the required MCLK frequency, are illustrated in

through

.

Refer to

for the required SCLK timing associated with the selected Digital Interface Format and

to the

“Switching Specifications - Serial Audio Interface” section on page 10

frequencies.

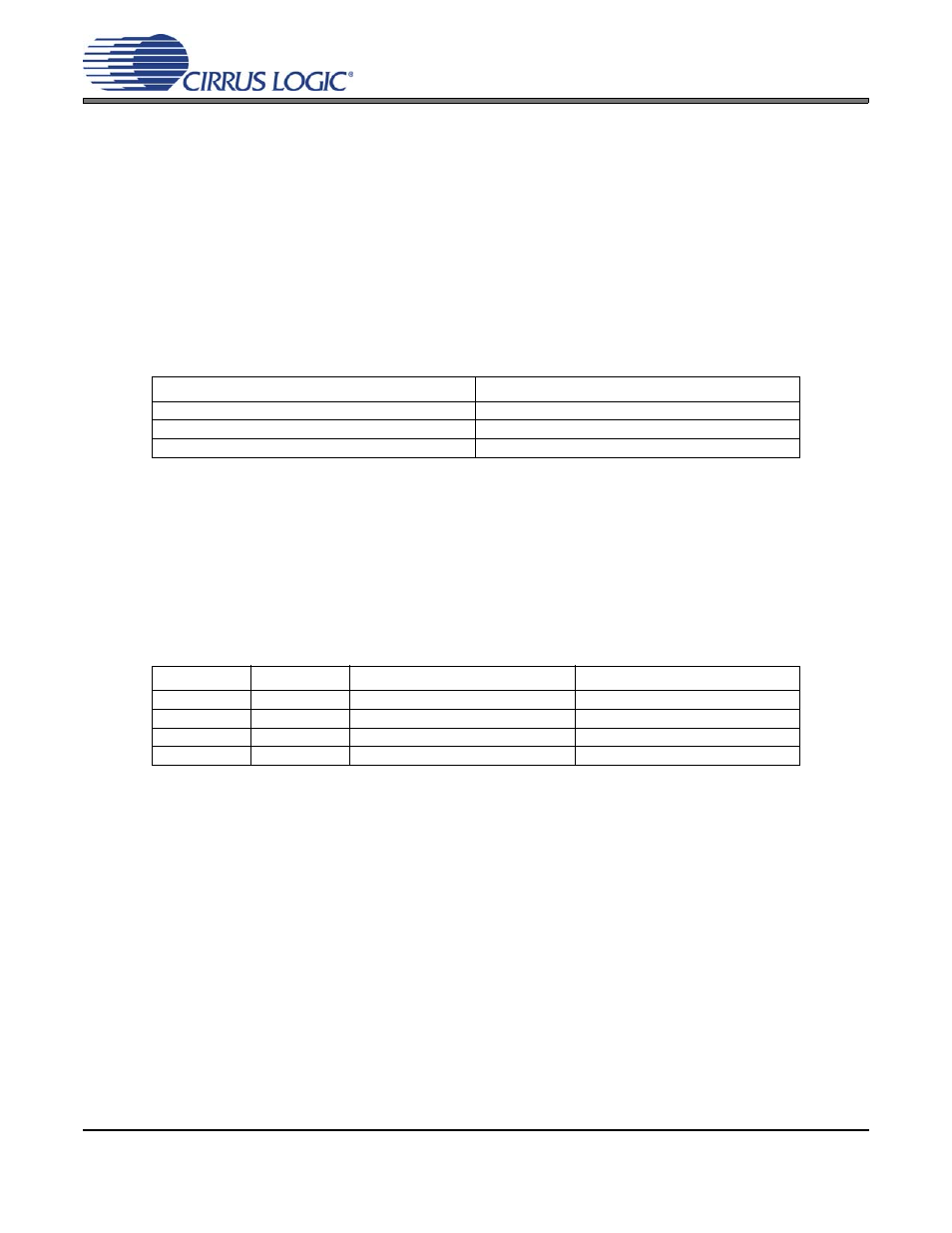

Input Sample Rate (F

S

)

MODE

4 kHz - 50 kHz

Single-Speed Mode

84 kHz - 100 kHz

Double-Speed Mode

170 kHz - 200 kHz

Quad-Speed Mode

Table 1. CS4351 Auto-Detect

FM1

FM0

Input Sample Rate (F

S

)

MODE

0

0

Auto speed mode detect

Auto

0

1

4 kHz - 50 kHz

Single-Speed Mode

1

0

50 kHz - 100 kHz

Double-Speed Mode

1

1

100 kHz - 200 kHz

Quad-Speed Mode

Table 2. CS4351 Mode Select