5 voltage reference, 1 vref_mod, 2 common mode bias – Cirrus Logic CDB5378 User Manual

Page 22: 3 digital hardware, 1 digital filter, Cdb5378

CDB5378

22

DS639DB4

2.2.5

Voltage Reference

A voltage reference on CDB5378 creates a precision voltage from the regulated analog supplies for the

CS5373A VREF input. Because the voltage reference output is generated relative to the negative analog

power supply, VREF+ is near GND potential for bipolar power supplies.

2.2.5.1

VREF_MOD

The voltage reference output is provided to the CS5373A modulator and test DAC through a low-pass RC

filter. By filtering the voltage reference input to the device, high-frequency noise is eliminated and any sig-

nal-dependent sampling of VREF is isolated. The voltage reference signal is routed as a differential pair

from the large RC filter capacitor to control the sensitive VREF source-return currents and keep them out

of the ground plane. In addition to the RC filter function, the 100 uF filter capacitor provides a large charge-

well to help settle voltage reference sampling transients.

2.2.5.2

Common Mode Bias

A buffered version of the voltage reference is created as a low-impedance common mode bias source for

the analog signal inputs. The bias resistors connected between the buffered voltage reference and each

analog signal input half depends on the sensor type and should be modified to match the sensor manu-

facturer recommendations.

2.3

Digital Hardware

2.3.1

Digital Filter

The CS5378 digital filter performs filtering and decimation of the

∆Σ bit stream from the CS5373A modu-

lator. It also creates a

∆Σ test bit stream output to create analog test signals in the CS5373A DAC.

The CS5378 requires several control signal inputs from the external system.

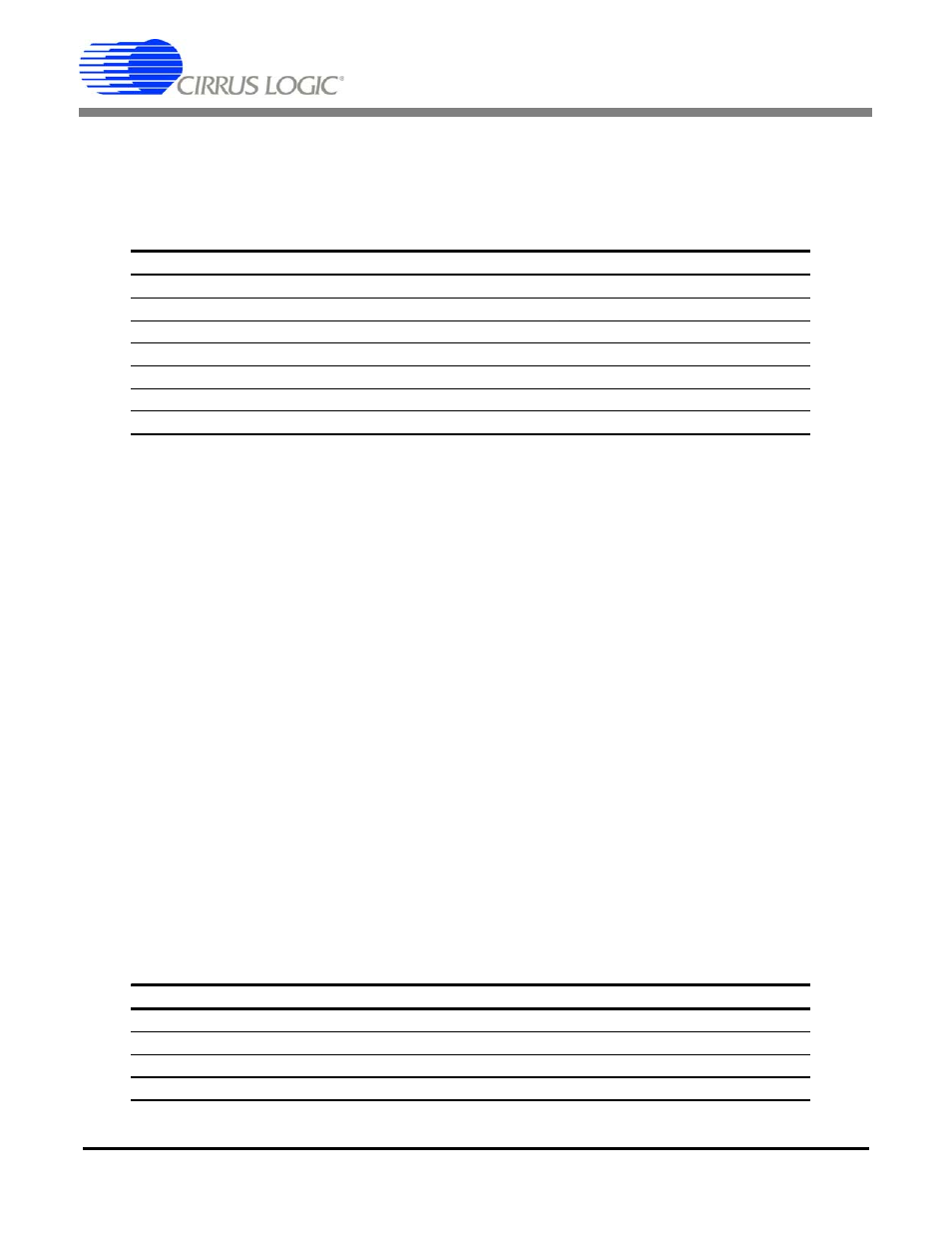

Specification Value

Precision Reference - Linear Tech

LT1019AIS8-2.5

Surface Mount Package Type

SO-8

Output Voltage Tolerance

+/- 0.05%

Temperature Drift

10 ppm / degC

Quiescent Current

0.65 mA

Output Voltage Noise, 10 Hz - 1 kHz

4 ppm

RMS

Ripple Rejection, 10 Hz - 200 Hz

> 100 dB

Control Signals

Description

CLK

Master clock input.

RESETz

Reset input, active low

SYNC

Master synchronization input, rising edge triggered

TIMEB

Time Break input, rising edge triggered