Packet processor b, Switchblade x8100 series | system overview – Allied Telesis SwitchBlade x8100 Series User Manual

Page 14

| SwitchBlade x8100 Series System Overview

alliedtelesis

.com

14

SwitchBlade x8100 Series

| System Overview

CPU traffic prioritization and rate limiting

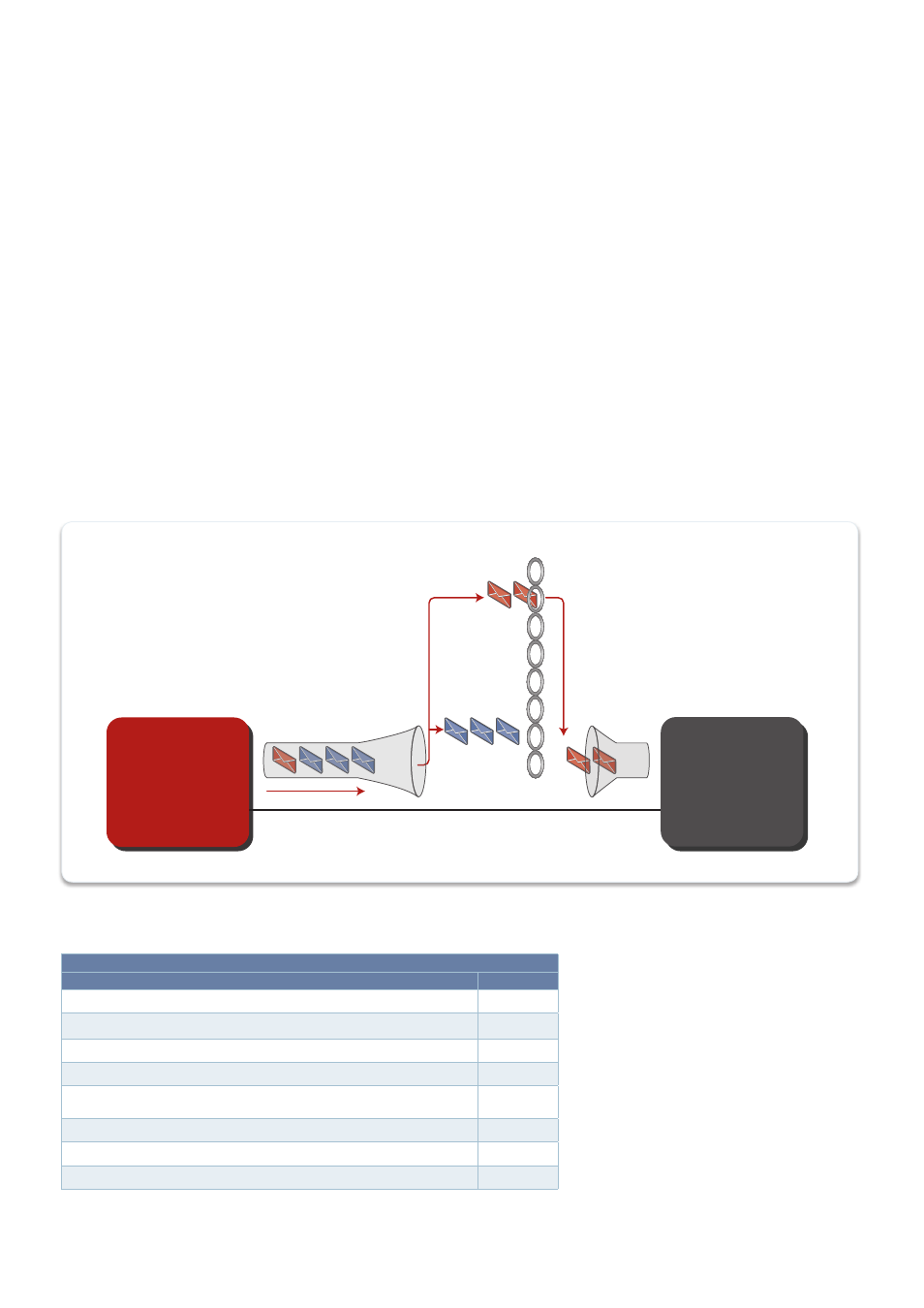

In a Layer 3 switch, such as the SwitchBlade x8100 Series, data traffic will be predominantly switched in hardware by the packet

processors, keeping wire-speed performance for the large number of gigabit and 10 gigabit ports.

Control plane traffic is processed by the CPU, as it manages internal switch management. Some data plane traffic will also be required

to be processed by the CPU on the master CFC, such as protocol management traffic (e.g. EPSR, LACP, STP, OSPF etc) and responses

to traffic destined for the switch itself (e.g. ARP replies etc). Any time traffic is trapped to the CPU it goes to the CPU on the master

CFC via a nominated packet processor (i.e. the first one on the master CFC) even if the trap was done by the line card.

To ensure timely processing of packets by the CPU on the master CFC, data plane traffic arriving at the CPU from the packet

processor is prioritized and there is a 30Mbps rate limit set to protect the CPU from being overloaded.

There are 8 queues that CPU bound traffic can be placed into. These queues are utilized to guarantee high priority packets that affect

network control and topology are always processed before lower priority traffic when the CPU is busy. For example, Layer-2 control

packets such as ESPR are placed in high priority queues by default. This ensures they will always receive service, even if the CPU is busy

with other lower priority traffic.

7

5

4

3

2

1

0

Traffic bound

for CPU

2 Gbps

Packet

Processor

B

CPU

Priority queues

cPU ingress PrioriTy qUeUes

ProTocol

cPU qUeUe

7

L2 Control Packets/EPSR/Loop Detect

6

DHCP Snooped Pkts

5

4

UC IPV6 Interface route

Link-local multicast protocols (OSPF/RIPv2/RIPng/PIM/VRRP/IGMP)

3

Default/ARP Reply/ARP Request/L2 unregistered MC

2

UC IPV4 Interface route

1

UC IPV4-6 Default route/L3 unregistered MC/sFlow Samples

0

The CPU priority queues used by the various protocols are shown in the table below.