4 chipset, Cpu tm function [enabled, Execute disable bit [enabled – Asus P5B SE User Manual

Page 81: Core multi-processing [enabled, Northbridge configuration, Allows you to use the enhanced intel, Speedstep

ASUS P5B SE

4-2

CPU TM function [Enabled]

Allows you to enable or disable the CPU internal thermal control function. In TM

mode, the CPU power consumption is reduced.

Configuration options: [Disabled] [Enabled]

Execute Disable Bit [Enabled]

Allows you to enable or disable the No-Execution Page Protection Technology.

Setting this item to [Disabled] forces the XD feature flag to always return to zero

(0). Configuration options: [Disabled] [Enabled]

Core Multi-processing [Enabled]

Allows you to enable or disable the Core Multi-processing function.

Configuration options: [Disabled] [Enabled]

Enhanced Intel(R) SpeedStep Technology (EIST) [Enabled]

Allows you to use the Enhanced Intel

®

SpeedStep

®

Technology. When set to

[Enabled], you can adjust the system power settings in the operating system to

use the EIST feature. Set this item to [Disabled] if you do not want to use the EIST.

Configuration options: [Enableds] [Disabled]

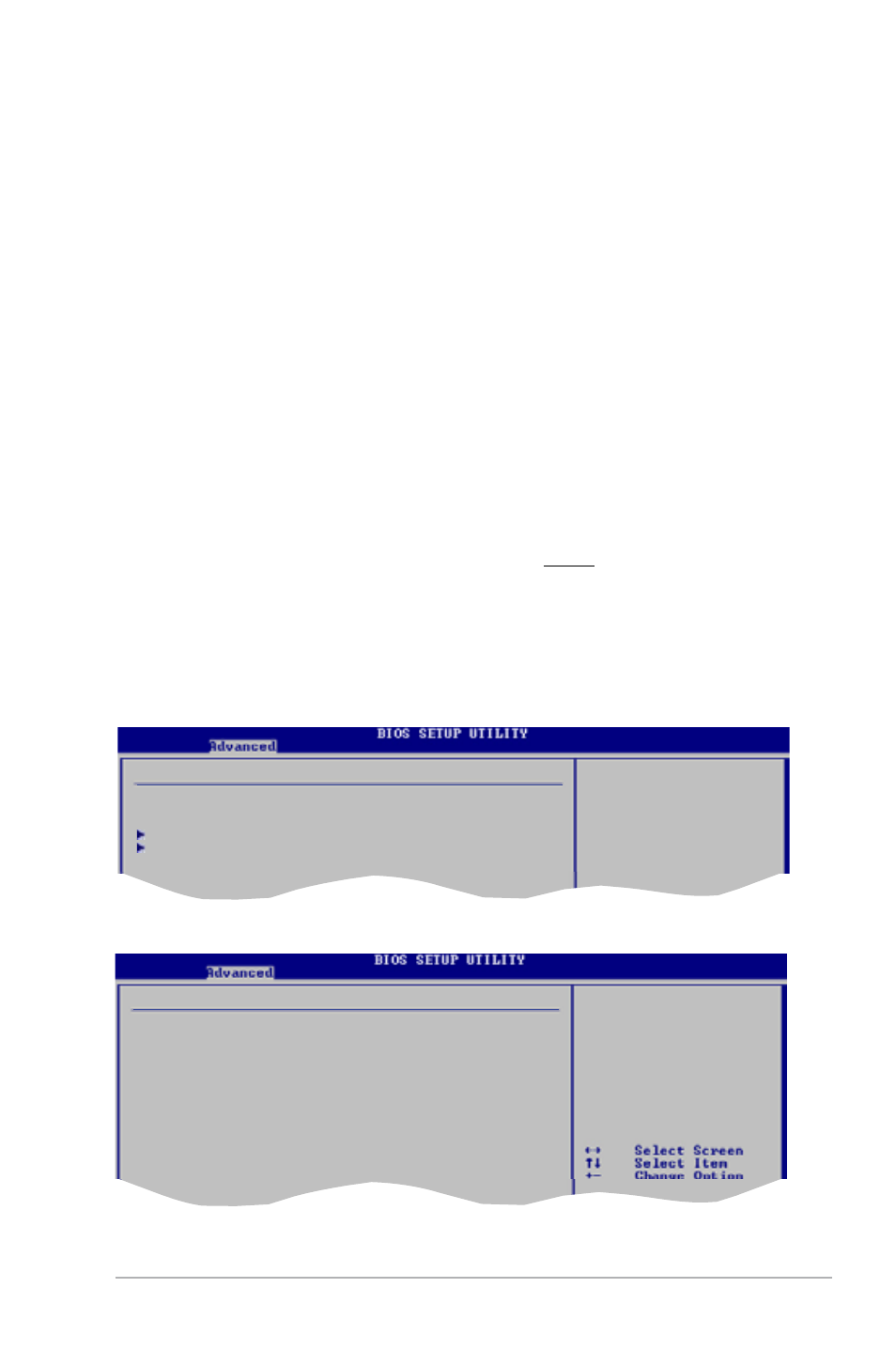

4.4.4

Chipset

The Chipset menu allows you to change the advanced chipset settings. Select an

item then press

Chipset Settings

WARNING: Setting wrong values in below sections

may cause the system to malfunction.

NorthBridge Configuration

SouthBridge Configuration

North Bridge Chipset Configuration

Memory Remap Feature

[Disabled]

DRAM Frequency

[Auto]

Configure DRAM Timing by SPD [Enabled]

DRAM 1N Mode Select

[Disabled]

Memory Hole

[Disabled]

Initiate Graphic Adapter

[PEG/PCI]

PEG Port Configuration

PEG Port

[Auto]

PEG Force x1

[Disabled]

NorthBridge Configuration