2 hshake register (0x35), Hshake register (0x35), Table 5-9: bist timeout period – PNI RM3100 Sensor Suite User Manual

Page 38: Table 5-10: bist lr periods

PNI Sensor Corporation

Doc 1017252 r03

RM3100 & RM2100 Sensor Suite User Manual

Page 37 of 45

Where:

STE – Setting this to ‘1’ commands the MagI2C to run the built-in self test when

the POLL register is written to. The end of the built-in self test sequence will be

indicated by DRDY going HIGH.

ZOK, YOK, and XOK – These read-only bits indicate whether or not the X, Y,

and Z LR oscillators functioned correctly during the built-in self test. A ‘1’

indicates a properly function oscillator. Note that STE also should be HIGH

when this is read, or the reading is invalid.

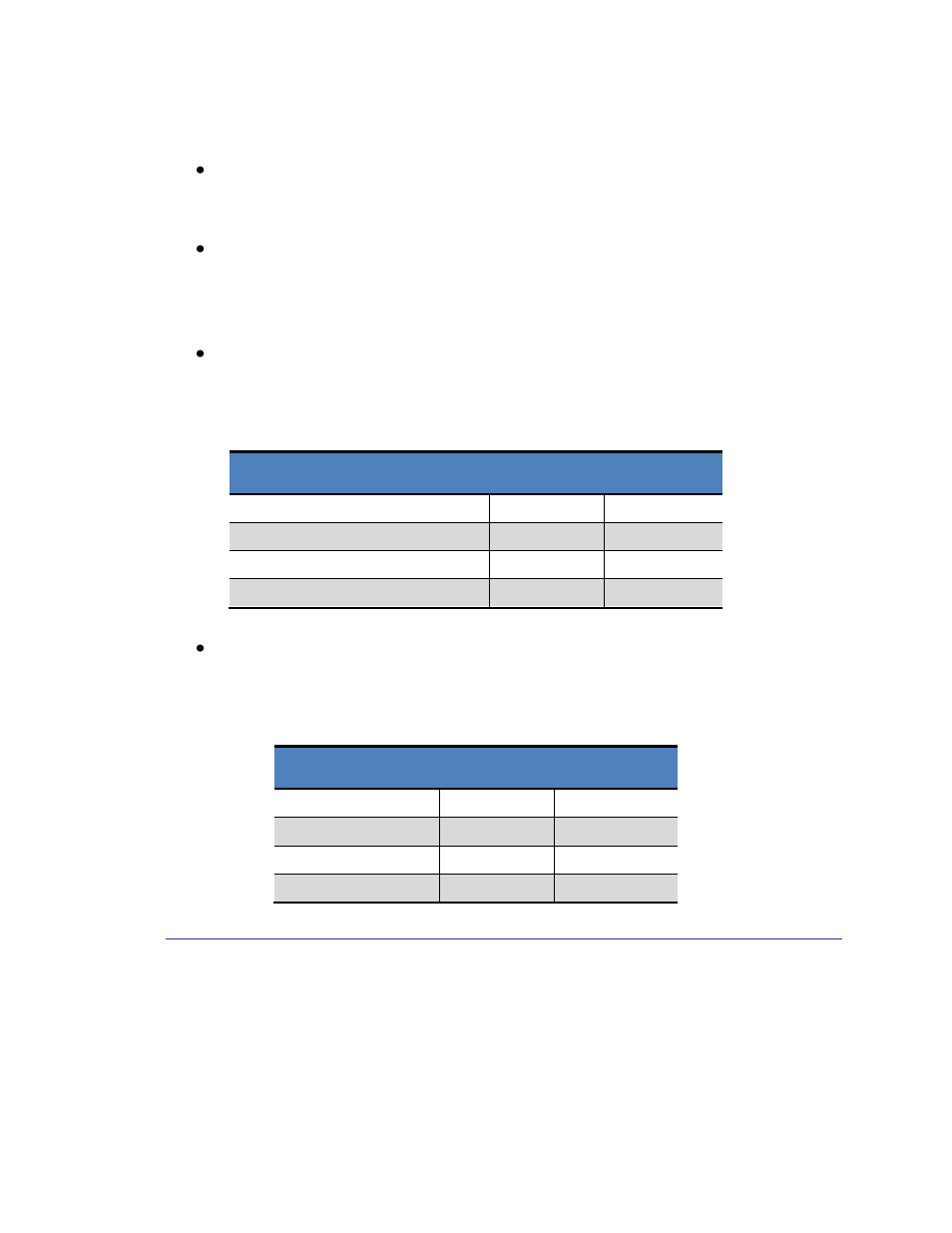

BW – These two bits define the timeout period for the LR oscillator periods, as

Table 5-9: BIST Timeout Period

BIST Wait Time

BW1

BW0

Unused

0

0

1 Sleep Oscillation Cycle (30 µs)

0

1

2 Sleep Oscillation Cycles (60 µs)

1

0

4 Sleep Oscillation Cycles (120 µs)

1

1

BP – These two bits define the number of LR periods for measurement during the

built-in self test, as given in Table 5-10.

Table 5-10: BIST LR Periods

BIST LR Periods

BW1

BW0

Unused

0

0

1 LR Period

0

1

2 LR Periods

1

0

4 LR Periods

1

1

5.6.2 HSHAKE Register (0x35)

The HSHAKE register is used to set conditions for clearing the DRDY pin and for

determining why a register command was not fulfilled. Write to the HSHAKE register

by sending 0x35 followed by the BIST register values, and request a read from the

HSHAKE register by sending 0xB5. The register contents are defined below.