Teledyne LeCroy QPHY-LPDDR2 User Manual

Page 48

48

QPHY-LPDDR2-OM-G Rev B

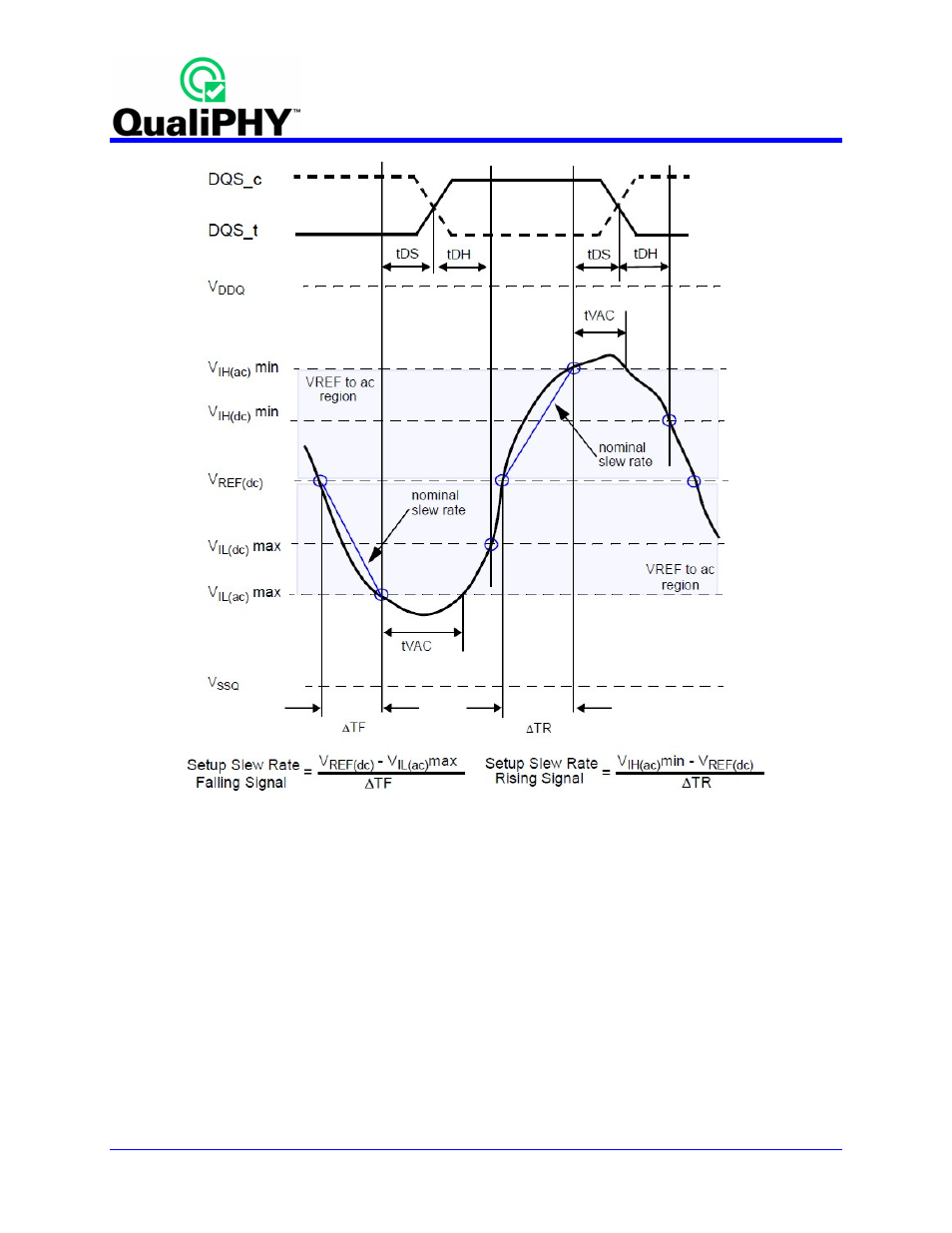

Figure 27. Slew Rate [JESD209-2D figure 124]

DQS and DQS# signals must be monotonic between VIL(dc)max and VIH(dc)min.

Hold (tDH) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of

VIL(dc)max and the first crossing of VREF(dc). Hold (tDH) nominal slew rate for a falling signal is defined

as the slew rate between the last crossing of VIH(dc)min and the first crossing of VREF(dc).

tIS(base) - Address and Control Input Setup Time

Input waveform timing is referenced from the input signal crossing at the VIH(ac)min level to the

differential clock crosspoint at VREF for a rising signal, and from the input signal crossing at the

VIL(ac)max level to the differential clock crosspoint at VREF for a falling signal applied to the device

under test. See table below.

- WaveAce EasyScope Operators Manual (28 pages)

- PeRT3 Software Interface (15 pages)

- FireInspector Automation Application Programming Interface (92 pages)

- PETracer ProtoSync Software User Manual (154 pages)

- QPHY-PCIe3-Tx-Rx (32 pages)

- Signal Integrity Studio (14 pages)

- Serial Data Debug Solutions (204 pages)

- Line Code and Symbolic Decoders (20 pages)

- AORM - Advanced Optical Recording Measurements (125 pages)

- CANbus TD - Quick Reference Guide (8 pages)

- CANbus TD and CANbus TDM - Operators Manual (69 pages)

- FlexRay Trigger, Decode and Physical Layer Test (32 pages)

- MIPI D-PHY (15 pages)

- DFP2 - Digital Filter Package 2 (22 pages)

- ET-PMT - Electrical Telecom Pulse Mask Testing (11 pages)

- ENETbusD Decoder (16 pages)

- Eye Doctor II (45 pages)

- JitKit (16 pages)

- JTA2 (31 pages)

- Power Analyzer Package (34 pages)

- QPHY-10GBase-KR (28 pages)

- QPHY-10GBase-T (36 pages)

- QPHY-BroadR-Reach (33 pages)

- QPHY-DDR2 (47 pages)

- QPHY-DDR3 (44 pages)

- QPHY-DDR4 (73 pages)

- QPHY-DisplayPort (19 pages)

- QPHY-ENET (78 pages)

- QPHY-HDMI (37 pages)

- QPHY-MIPI-DPHY (32 pages)

- QPHY-MOST150 (24 pages)

- QPHY-MOST50 (21 pages)

- QPHY-PCIe (30 pages)

- QPHY-PCIE3 (28 pages)

- QPHY-SAS2 (45 pages)

- QPHY-SAS3 (50 pages)

- QPHY-SATA (45 pages)

- QPHY-USB (66 pages)

- QPHY-USB3-Tx-Rx (47 pages)

- QPHY-UWB (30 pages)

- SDA II (38 pages)

- SDA III-CompleteLinQ (59 pages)

- Spectrum Analyzer (14 pages)

- USB2 Decoder (24 pages)