Control and status registers defined, Control and status name definition – Impulse ACB-104.ULTRA (3514) User Manual

Page 11

© Sealevel Systems, Inc.

- 9 -

ACB-104.ULTRA User Manual

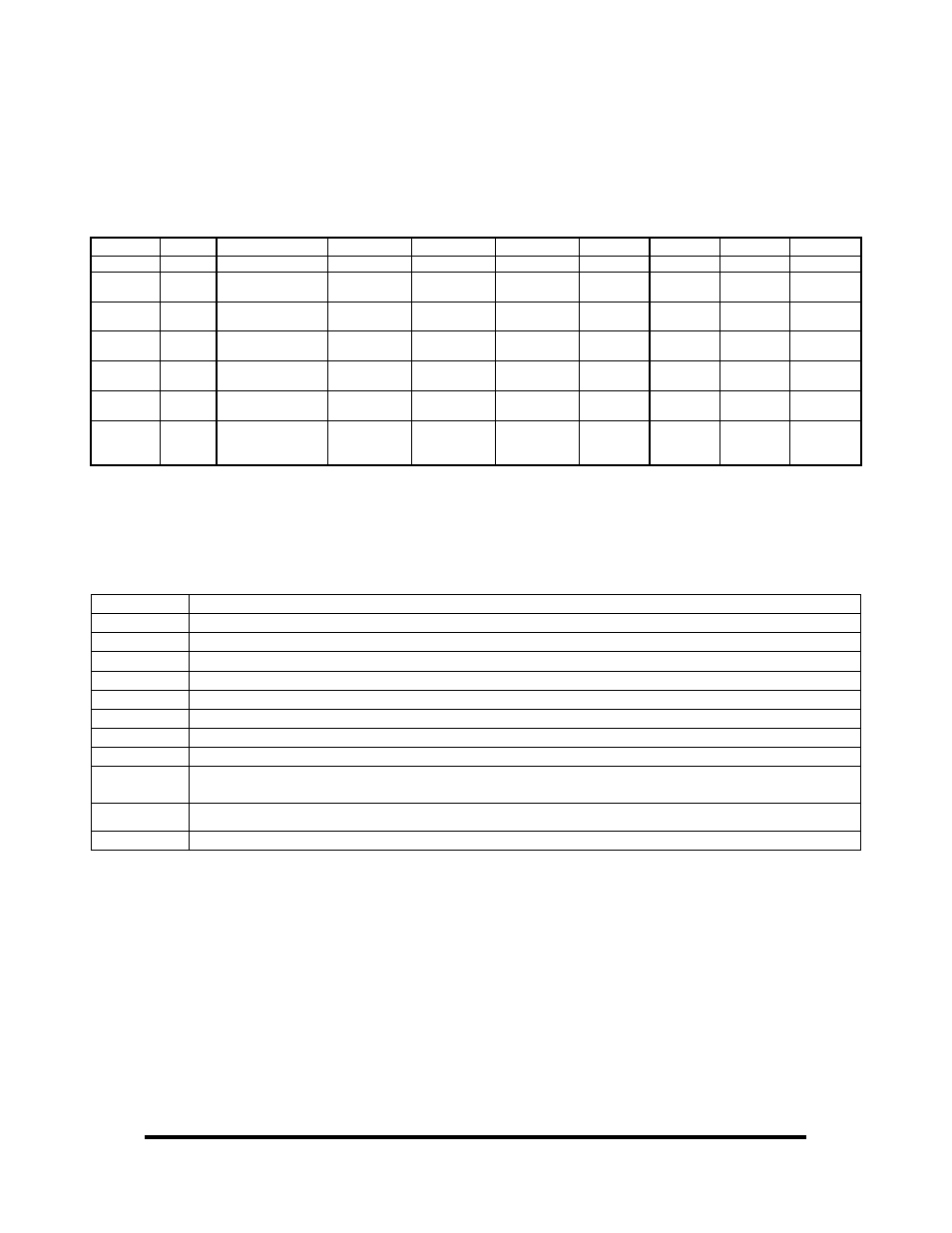

Control and Status Registers Defined

The control and status registers occupy 8 consecutive locations. The following tables

provide a functional description of the bit positions.

Address Mode

D7

D6

D5

D4 D3 D2 D1 D0

Base+0

RD {0}

{0} {0} {1}+

P17

P16

P15

P14

Base+0

WR ACCEN MEM/IUC X

X

P17 P16 P15 P14

Base+1

RD {0}

{0} {0} {0}

{0}

{0}

{0}

{0}

Base+1

WR

X

X X X

X

X

X

X

Base+2

RD LIN/PAGED

{0}

{1}

{0} {0} {0} {0} {0}

Base+2

WR

LIN/PAGED

X X X

X

X

X

X

Base+3

RD

{0}

{0} INTPEND

RESTAT

{1} {0} {0} {0}

Base+3

WR

SW Board Reset

X

X

X

X

X

X

X

Base+4

RD {0} IRQEN

{0} {0}

{0}

{0}

{0}

{0}

Base+4

WR X

IRQEN X

X X X X X

Base+5

RD

LL

RL

{0}

{0} M3 M2 M1 M0

Base+5

WR

LL

RL

X

X M3 M2 M1 M0

Base+6

RD SD7

SD6 SD5 SD4

SD3

SD2

SD1

SD0

Base+7

RD SD15

SD14 SD13 SD12 SD11

SD10 SD9 SD8

X = do not care

{ }= always this value

Control and Status Name Definition

Field Description

ACCEN

1 = Host access to RAM or IUSC enabled; 0 = Host access to RAM or IUSC disabled. (0 on power-up)

MEM/IUC

1 = Enable Host access to RAM; 0 = Enable Host access to IUSC. (0 on power-up)

P17-P14

These bits select which of sixteen 16K RAM pages is visible at the address selected by MA18-MA14.

IRQEN

1 = Interrupts enabled, 0 = Interrupts disabled. (0 on power-up)

INTPEND

IUSC interrupt status: 1 = No interrupt pending on IUSC; 0 = Interrupt pending on IUSC.

RESTAT

Reset status: 1 = On-board reset inactive; 0 = On-board reset active.

RL

Remote loopback

LL

Local loopback

M0-M3

I/O mode select to SP505 (all 0 on power-up)

See Interface Selection table for valid interface options

SD0-SD15

Optional security feature. Unique value per customer or application. (default value = FFFF)

LIN/PAGE

1=256K linear block in high memory only, 0=16X16K pages in low or high memory, (0 on power-up)