Inputs and outputs – Atec Anritsu-MG3690 Series User Manual

Page 13

13

Inputs and Outputs*

*Connectors may be available but not active, if option is not ordered.

** Options (7 & 18), (7 & 20), (8 & 9) are mutually exclusive, as they share the same

rear panel space.

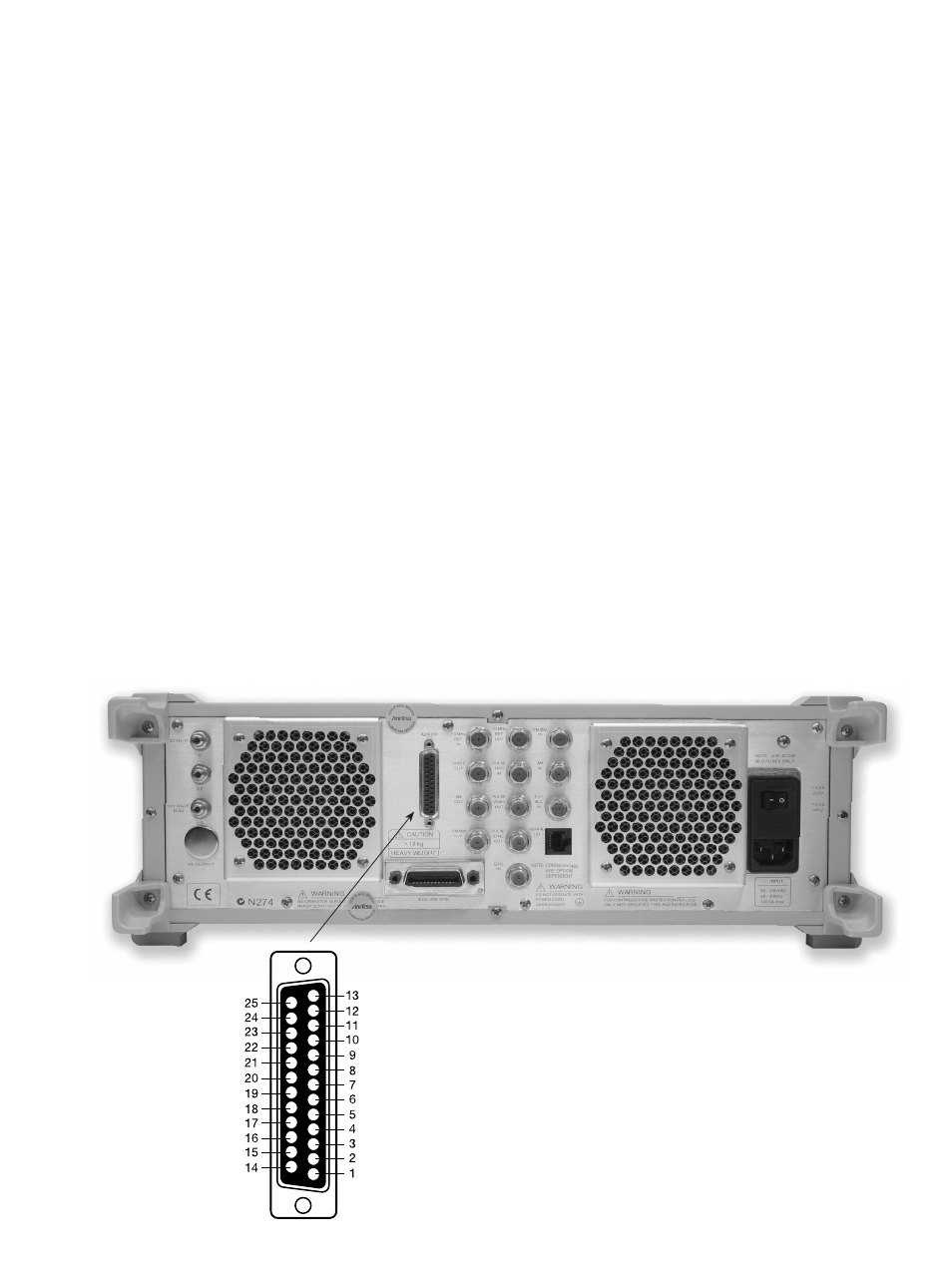

MG3690C Rear Panel

EXT ALC IN

Provides for leveling the RF output signal externally with

either a detector or power meter. Signal requirements are

shown in the RF Output specifications. BNC type, rear panel.

RF OUTPUT**

Provides for RF output from 50 Ω source impedance.

(Option 9)

Option 9 moves the RF Output connector from the front to the

rear panel. K Connector (female) fmax ≤ 40 GHz V Connector

(female) fmax ≥ 40 GHz.

10 MHz REF IN

Accepts an external 10 MHz ± 50 Hz, 0 dBm to +20 dBm

time-base signal. Automatically disconnects the internal

high-stability time-base option, if installed. 50 Ω impedance.

BNC type, rear panel.

10 MHz REF OUT

Provides a 1 Vp-p, AC coupled, 10 MHz signal derived from

the internal frequency standard. 50 Ω impedance. BNC

type, rear panel.

100 MHz REF IN

Accepts the 100 MHz signal from an MG3690C with

(Option 36)

Option 36 for ultra-stable phase tracking.

100 MHz REF OUT

Provides the 100 MHz signal for an MG3690C with

(Option 36)

Option 36 ultra-stable phase tracking.

HORIZ OUT

Provides 0V at beginning and +10V at end of sweep,

(Horizontal Sweep Output) regardless of sweep width. In CW mode, the voltage is

proportional to frequency between 0V at low end and +10V at

the high end of range. In CW mode, if CW RAMP is enabled, a

repetitive, 0V to +10V ramp is provided. BNC type, rear panel.

EFC IN

Provides the capability to frequency modulate the internal

crystal oscillator, allowing phase locking the synthesizer

inside an external lock loop. Specifications on page 2. BNC

type, rear panel.

AUX I/O

Provides for most of the rear panel BNC connections

(Auxiliary Input/Output)

through a single, 25-pin, D type connector. Supports

master-slave operation with another synthesizer or allows

for a single-cable interface with the Model 56100A Scalar

Network Analyzer and other Anritsu instruments (see figure

below). 25 pin D-type, rear panel.

SERIAL I/O

Provides access to RS-232 terminal ports to support

service and calibration functions and master-slave

operations. RJ45 type, rear panel.

IEEE-488 GPIB

Provides input/output connections for the General Purpose

Interface Bus (GPIB). Type 57, rear panel.

mmW BIAS**

Provides the bias for the external waveguide multipliers for

(Option 18)

coverage up to 325 GHz. Twinax, rear panel.

RF, LO, IF**

Provides access to an internal IF up-conversion mixer.

(Option 7)

K Connector (female) 3X, rear panel.

PULSE TRIG IN

Accepts an external TTL compatible signal to pulse

(Option 26)

modulate the RF output signal or to trigger or to gate the

optional internal pulse generator. BNC type, rear panel.

PULSE SYNC OUT

Provides a TTL compatible signal, synchronized to the

(Option 27)

internal pulse modulation output. BNC type, rear panel.

PULSE VIDEO OUT

Provides a video modulating signal from the internal pulse

(Option 27)

generator. BNC type, rear panel.

AM IN

Accepts an external signal to amplitude modulate the

(Option 14)

RF output signal, 50 Ω impedance. BNC type, rear panel.

FM/ΦM IN

Accepts an external signal to frequency or phase modulate

(Option 12)

the RF output signal. 50 Ω impedance. BNC type, rear panel.

AM OUT

Provides the amplitude modulation waveform from the

(Option 27)

internal LF generator. BNC type, rear panel.

FM/ΦM OUT

Provides the frequency or phase modulation waveform from

(Option 27)

the internal LF generator. BNC type, rear panel.

SCAN MOD IN**

Accepts an external signal to scan modulate the RF output

(Option 20)

signal. High Impedance. BNC type, rear panel.

POWER MONITOR IN

Accepts an external detector for power monitoring. Custom

(Option 8)

type, rear panel.

Aux I/O pins:

1. Horizontal Output

2. Chassis Ground

3. Sequential Sync Output

4. Low Alternate Enable Output

5. Marker Output

6. Retrace Blanking Output

7. Low Alternate Sweep Output

8. Chassis Ground

9. -

10. Sweep Dwell Output

11. Lock Status Output

12. Penlift

13. External Trigger Input

14. V/GHz Output

15. End-of-Sweep Input

16. End-of-Sweep Output

17. -

18. Sweep Dwell Input

19. -

20. Bandswitch Blanking Output

21. Master Reset

22. Horizontal Sweep Input

23. Horizontal Sweep Input Return

24. Chassis Ground

25. Memory Sequencing Input