Extended control register 4b – Rainbow Electronics DDS1693 User Manual

Page 20

DS1689/DS1693

20 of 32

VRT2 - This status bit gives the condition of the auxiliary battery. It is set to a logic 1 condition when the

external lithium battery is connected to the V

BAUX

. If this bit is read as a logic 0, the external battery

should be replaced.

INCR - Increment in Progress status bit. This bit is set to a 1 when an increment to the time/date registers

is in progress and the alarm checks are being made. INCR will be set to a 1 at 122

ms before the update

cycle starts and will be cleared to 0 at the end of each update cycle.

PAB - Power Active Bar control bit. When this bit is 0, the

PWR

pin is in the active low state. This bit

can be written to a logic 1 or 0 by the user. If either WF AND WIE = 1 OR KF AND KSE = 1, the PAB

bit will be cleared to 0.

RF - Ram Clear Flag - This bit will be set to a logic 1 when a high to low transition occurs on the

RCLR

input if RCE=1. The RF bit is cleared by writing it to a logic 0. This bit can also be written to a logic 1 to

force an interrupt condition.

WF – Wake-up Alarm Flag - This bit is set to 1 when a wake-up alarm condition occurs or when the user

writes it to a 1. WF is cleared by writing it to a 0.

KF - Kickstart Flag - This bit is set to a 1 when a kickstart condition occurs or when the user writes it to a

1. This bit is cleared by writing it to a logic 0.

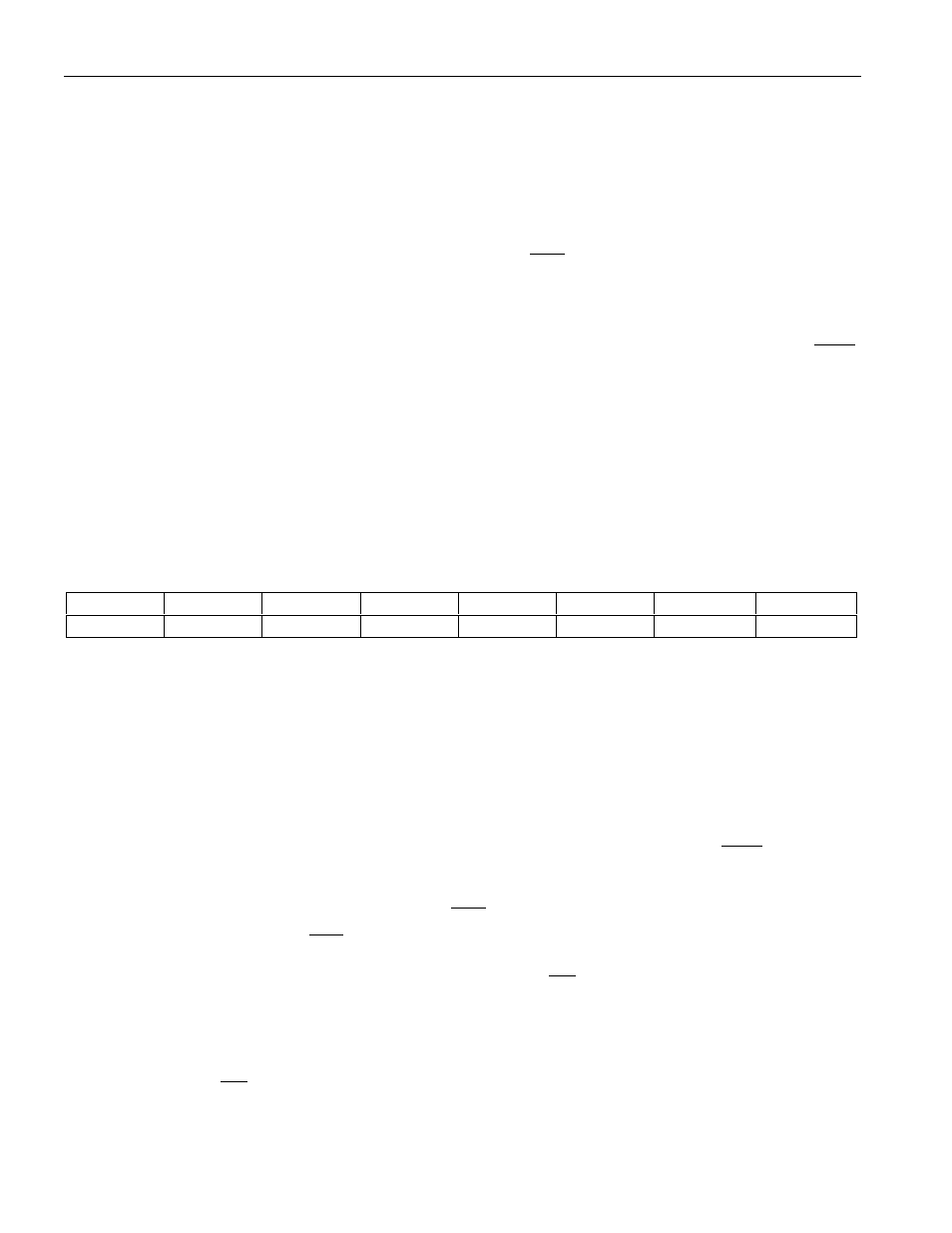

EXTENDED CONTROL REGISTER 4B

MSB LSB

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

ABE

E32K

CS

RCE

PRS

RIE

WIE

KSE

ABE - Auxiliary Battery Enable. This bit when written to a logic 1 will enable the V

BAUX

pin for

extended functions.

E32K - Enable 32,768 output. This bit when written to a logic 1 will enable the 32,768 Hz oscillator

frequency to be output on the SQW pin provided SQWE=1.

CS - Crystal Select Bit. When CS is set to a 0, the oscillator is configured for operation with a crystal that

has a 6 pF specified load capacitance. When CS=1, the oscillator is configured for a 12.5 pF crystal.

RCE - RAM Clear Enable bit. When set to a 1, this bit enables a low level on pin 4 (

RCLR

) to clear all

114 bytes of user RAM. When RCE = 0, the RAM clear function is disabled.

PRS - PAB Reset Select Bit. When set to a 0 the

PWR

pin will be set hi-Z when the DS1689 goes into

power-fail. When set to a 1, the

PWR

pin will remain active upon entering power-fail.

RIE - Ram Clear Interrupt Enable. When RIE is set to a 1, the

IRQ

pin will be driven low when a RAM

clear function is completed.

WIE – Wake-Up Alarm Interrupt Enable. When V

CC

voltage is absent and WIE is set to a 1, the PWR pin

will be driven active low when a wake-up condition occurs, causing the WF bit to be set to 1. When V

CC

is then applied, the

IRQ

pin will also be driven low. If WIE is set while system power is applied, both