Ram clear, Extended control registers, Extended control register 4a – Rainbow Electronics DDS1693 User Manual

Page 19

DS1689/DS1693

19 of 32

addition, the other possible interrupt sources within the DS1689/DS1693 may cause

IRQ

to be driven

low. While system power is applied, the on chip logic will always attempt to drive the

PWR

pin active in

response to the enabled kickstart or wake-up condition. This is true even if

PWR

was previously inactive

as the result of power being applied by some means other than wake-up or kickstart.

The system may be powered down under software control by setting the PAB bit to a logic 1. This causes

the open-drain

PWR

pin to be placed in a high impedance state, as shown at the beginning of interval 4 in

the timing diagram. As V

CC

voltage decays, the

IRQ

output pin will be placed in a high impedance state

when V

CC

goes below V

PF

. If the system is to be again powered on in response to a wake-up or kickstart,

then the both the WF and KF flags should be cleared and WIE and/or KSE should be enabled prior to

setting the PAB bit.

During interval 5, the system is fully powered down. Battery backup of the clock calendar and

nonvolatile RAM is in effect,

PWR

and

IRQ

are tri-stated, and monitoring of wake-up and kickstart takes

place.

RAM CLEAR

The DS1689/DS1693 provides a RAM clear function for the 114 bytes of user RAM. When enabled, this

function can be performed regardless of the condition of the V

CC

pin.

The RAM clear function is enabled or disabled via the RAM Clear Enable bit (RCE; bank 1, register

04BH). When this bit is set to a logic 1, the 114 bytes of user RAM will be cleared (all bits set to 1)

when an active low transition is sensed on the

RCLR

pin. This action will have no effect on either the

clock/calendar settings or upon the contents of the external extended RAM. The RAM clear Flag (RF,

bank 1, register 04BH) will be set when the RAM clear operation has been completed. If V

CC

is present at

the time of the RAM clear and RIE=1, the

IRQ

line will also be driven low upon completion. The

interrupt condition can be cleared by writing a 0 to the RF bit. The

IRQ

line will then return to its inactive

high level provided there are no other pending interrupts. Once the

RCLR

pin is activated, all read/write

accesses are locked out for a minimum recover time, specified as t

REC

in the Electrical Characteristics

section.

When RCE is cleared to 0, the RAM clear function is disabled. The state of the

RCLR

pin will have no

effect on the contents of the user RAM, and transitions on the

RCLR

pin have no effect on RF.

EXTENDED CONTROL REGISTERS

Two extended control registers are provided to supply controls and status information for the extended

features offered by the DS1689/DS1693. These are designated as extended control registers A and B and

are located in register bank 1, locations 04AH and 04BH, respectively. The functions of the bits within

these registers are described as follows.

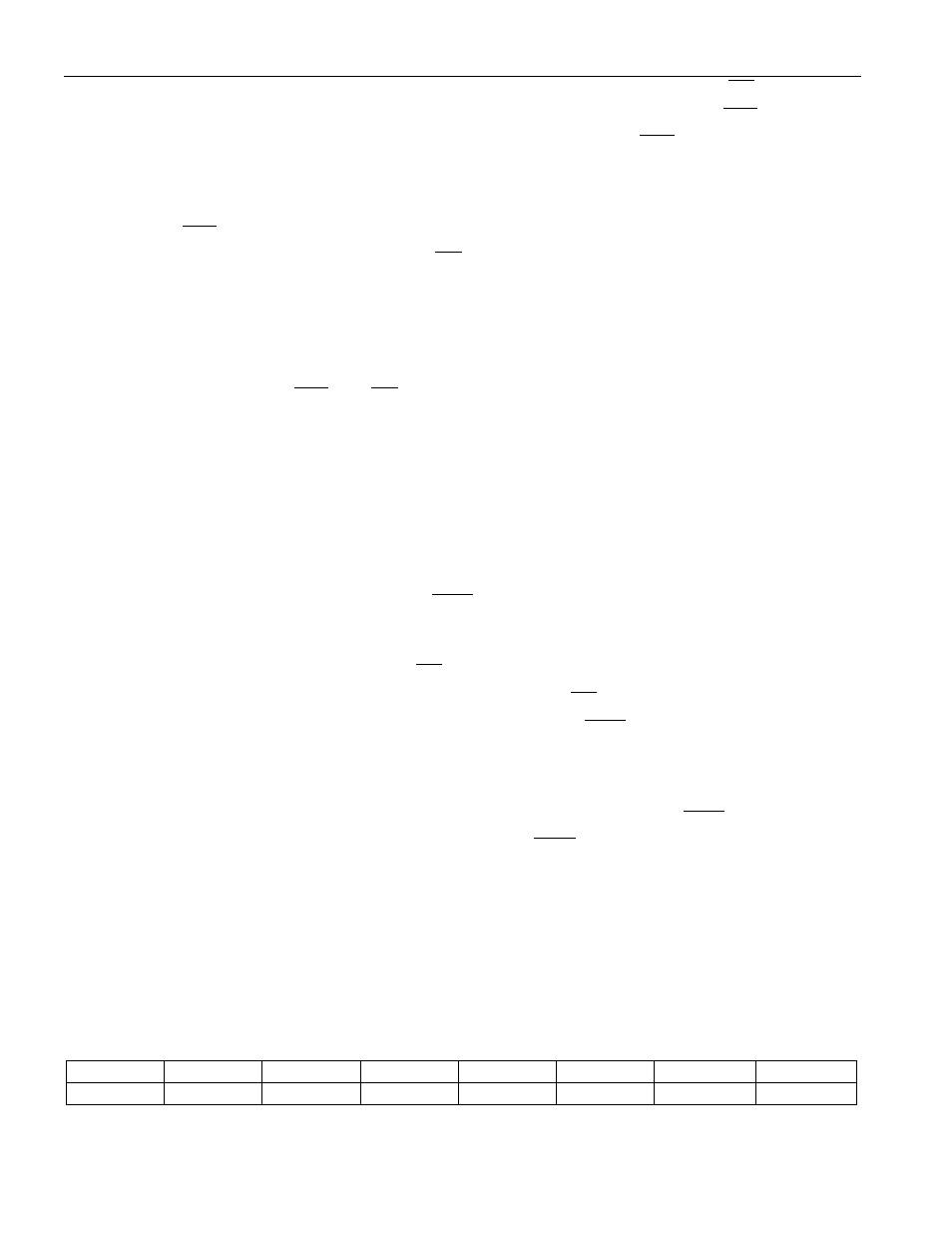

EXTENDED CONTROL REGISTER 4A

MSB LSB

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

VRT2

INCR

*

*

PAB

RF

WF

KF