Max3580 direct-conversion tv tuner, Detailed description, Table 2. register configuration – Rainbow Electronics MAX3580 User Manual

Page 12: Programmable registers, Register description

MAX3580

Direct-Conversion TV Tuner

12

______________________________________________________________________________________

Detailed Description

Programmable Registers

The MAX3580 includes thirteen write/read registers and

three read-only registers. See Table 2 for register con-

figuration and the

Register Description

section. The

register configuration of Table 2 shows each bit name

and the bit usage information for all registers. “U”

labeled under each bit name indicates that the bit

value is user defined to meet specific application

requirements. A “0” or “1” indicates that the bit must be

set to the defined “0” or “1” value for proper operation.

Operation is not tested or guaranteed if these bits are

programmed to other values and is only for

factory/bench evaluation. For field use, always program

to the defined operational state. Note that all registers

must be written after and no earlier than 100µs after

device power-up.

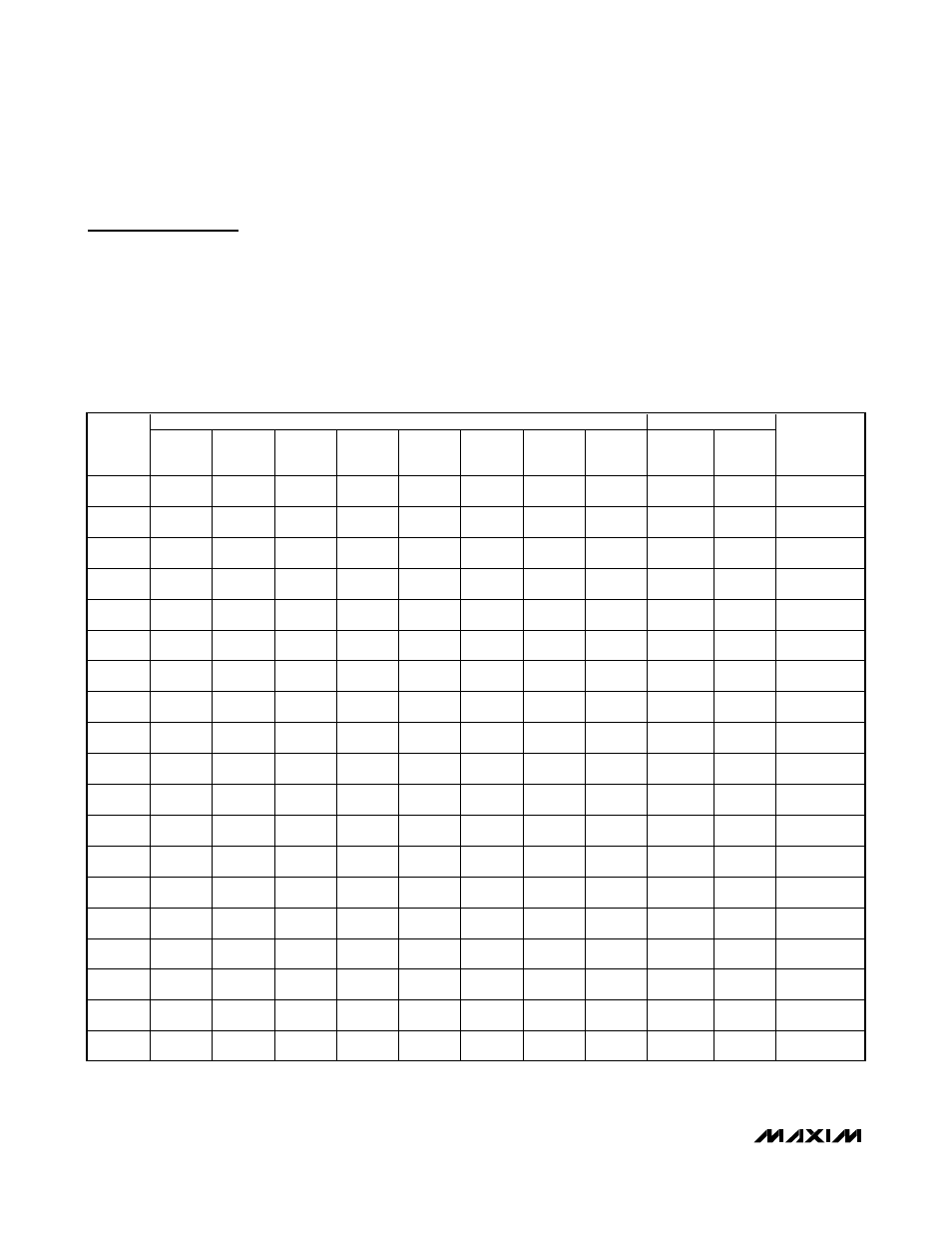

Table 2. Register Configuration

8-BIT DATA

REGISTER SETTINGS

REGISTER

ADDRESS

D7

D6

D5

D4

D3

D2

D1

D0

OPERATION

DEFINED

DEFAULT

SETTINGS

(POR)

REGISTER

NAME

0x00

N7

U

N6

U

N5

U

N4

U

N3

U

N2

U

N1

U

N0

U

—

H17

N-Divider Integer

0x01

MP

0

LI1

0

LI0

0

INT

U

F19

U

F18

U

F17

U

F16

U

—

h18

N-Divider Frac2

0x02

F15

U

F14

U

F13

U

F12

U

F11

U

F10

U

F9

U

F8

U

—

h00

N-Divider Frac1

0x03

F7

U

F6

U

F5

U

F4

U

F3

U

F2

U

F1

U

F0

U

—

h00

N-Divider Frac0

0x04

TFS<7>

U

TFS<6>

U

TFS<5>

U

TFS<4>

U

TFS<3>

U

TFS<2>

U

TFS<1>

U

TFS<0>

U

—

hDB

Tracking Filter

Series Caps

0x05

VCO_DIV1

U

VCO_DIV0

U

RFS

U

TF_BS

U

TFP<3>

U

TFP<2>

U

TFP<1>

U

TFP<0>

U

—

h7C

Tracking Filter

Parallel Cap

0x06

RDIV

U

ICP

U

CPS

U

ADLY1

0

ADLY0

1

LF_DIV2

U

LF_DIV1

U

LF_DIV0

U

—

h0A

PLL Configuration

0x07

CP_TST2

0

CP_TST1

0

CP_TST0

0

X

0

TURBO

1

LD_MUX2

U

LD_MUX1

U

LD_MUX0

U

—

h08

Test Functions

0x08

X

0

SHDN_BG

U

SHDN_PD

U

SHDN_REF

U

SHDN_SYN

U

SHDN_MX

U

SHDN_BB

U

SHDN_RF

U

—

h00

Shutdown Control

0x09

VCO1

U

VCO0

U

BS2

U

BS1

U

BS0

U

VAS

1

ADL

0

ADE

0

—

hC0

VCO Control

0x0A

BB_BW3

U

BB_BW2

U

BB_BW1

U

BB_BW0

U

X

0

PD_TH2

U

PD_TH1

U

PD+TH0

U

—

h87

Baseband Control

0x0B

BB_BIA

0

DC_DAC8

0

DC_MO1

1

DC_MO0

1

DC_SP1

1

DC_SP0

0

DC_TH1

0

DC_TH0

0

h38

h40

DC Offset Control

0x0C

DC_DAC7

0

DC_DAC6

0

DC_DAC5

0

DC_DAC4

0

DC_DAC3

0

DC_DAC2

0

DC_DAC1

0

DC_DAC0

0

h00

h00

DC Offset DAC

0x0D

X

0

FUSE_TH

0

X

0

WR

0

TFA<3>

U

TFA<2>

U

TFA<1>

U

TFA<0>

U

—

h00

ROM Table

Address

0x0E

TFD<7>

0

TFD<6>

0

TFD<5>

0

TFD<4>

0

TFD<3>

0

TFD<2>

0

TFD<1>

0

TFD<0>

0

h00

h00

ROM Table Fuse

Data

0x0F

X

0

X

0

X

0

X

0

MX_HR<3>

0

MX_HR<2>

0

MX_HR<1>

0

MX_HR<0>

0

h00

h00

Mixer Harmonic

Rejection

0x10

TFR<7>

TFR<6>

TFR<5>

TFR<4>

TFR<3>

TFR<2>

TFR<1>

TFR<0>

N/A

N/A

ROM Table Data

Read Back

0x11

POR

VASA

VASE

LD

DC_LO

DC_HI

GKT

PD_OVLD

N/A

N/A

Chip Status Read

Back

0x12

VCO1A

VCO0A

BS2A

BS1A

BS0A

ADC2

ADC1

ADC0

N/A

N/A

Autotuner Read

Back