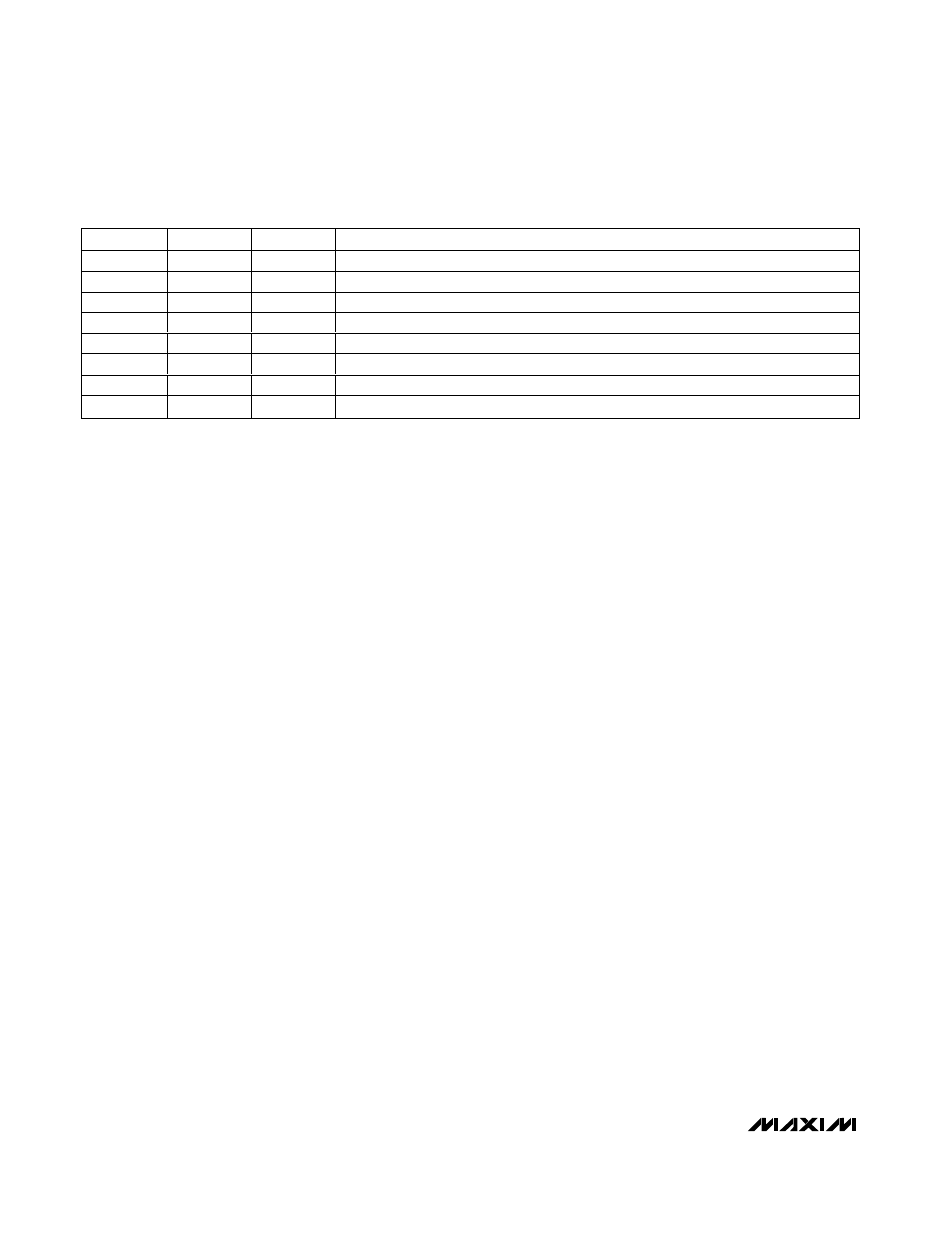

Table 8. mode-control bits m[2:0 – Rainbow Electronics MAX1301 User Manual

Page 24

MAX1300/MAX1301

External Acquisition Mode (Mode 1)

The slowest maximum throughput rate is achieved with

the external acquisition method. SCLK controls the

acquisition of the analog signal in external acquisition

mode, facilitating precise control over when the analog

signal is captured. The internal clock controls the con-

version of the analog input voltage. The analog input

sampling instant is at the falling edge of the 16th SCLK

(Figure 3).

For the external acquisition mode, CS must remain low

for the first 15 clock cycles and the rise on or after the

falling edge of the 16th SCLK cycle as shown in Figure

3. For optimal performance, idle DIN and SCLK during

the conversion. With careful board layout, transitions at

DIN and SCLK during the conversion have a minimal

impact on the conversion result.

After the conversion is complete, SSTRB asserts high

and CS can be brought low to read the conversion

result. SSTRB returns low on the rising SCLK edge of

the subsequent start bit.

Internal Clock Mode (Mode 2)

In internal clock mode, the internal clock controls both

acquisition and conversion of the analog signal. The inter-

nal clock starts approximately 100ns to 400ns after the

falling edge of the eighth SCLK and has a rate of about

4.5MHz. The analog input sampling instant occurs at the

falling edge of the 11th internal clock signal (Figure 4).

For the internal clock mode, CS must remain low for the

first seven SCLK cycles and then rise on or after the

falling edge of the eighth SCLK cycle. After the conver-

sion is complete, SSTRB asserts high and CS can be

brought low to read the conversion result. SSTRB returns

low on the rising SCLK edge of the subsequent start bit.

Reset (Mode 4)

As shown in Table 8, set M[2:0] = 100 to reset the

MAX1300/MAX1301 to its default conditions. The

default conditions are full power operation with each

channel configured for ±12V, bipolar, single-ended

conversions using external clock mode (mode 0).

Partial Power-Down Mode (Mode 6)

As shown in Table 8, when M[2:0] = 110, the device

enters partial power-down mode. In partial power-

down, all analog portions of the device are powered

down except for the reference voltage generator and

bias supplies.

To exit partial power-down, change the mode by issu-

ing one of the following mode-control bytes (see the

Mode Control section):

• External-Clock-Mode Control Byte

• External-Acquisition-Mode Control Byte

• Internal-Clock-Mode Control Byte

• Reset Byte

• Full Power-Down-Mode Control Byte

This prevents the MAX1300/MAX1301 from inadvertent-

ly exiting partial power-down mode because of a CS

glitch in a noisy digital environment.

Full Power-Down Mode (Mode 7)

When M[2:0] = 111, the device enters full power-down

mode and the total supply current falls to 1µA (typ). In

full power-down, all analog portions of the device are

powered down. When using the internal reference,

upon exiting full power-down mode, allow 10ms for the

internal reference voltage to stabilize prior to initiating a

conversion.

To exit full power-down, change the mode by issuing

one of the following mode-control bytes (see the Mode

Control section):

• External-Clock-Mode Control Byte

8-/4-Channel, ±12V Multirange Inputs,

Serial 16-Bit ADCs

24

______________________________________________________________________________________

M2

M1

M0

MODE

0

0

0

External Clock (DEFAULT)

0

0

1

External Acquisition

0

1

0

Internal Clock

0

1

1

Reserved

1

0

0

Reset

1

0

1

Reserved

1

1

0

Partial Power-Down

1

1

1

Full Power-Down

Table 8. Mode-Control Bits M[2:0]