Pin description – Rainbow Electronics MAX1301 User Manual

Page 12

MAX1300/MAX1301

8-/4-Channel, ±12V Multirange Inputs,

Serial 16-Bit ADCs

12

______________________________________________________________________________________

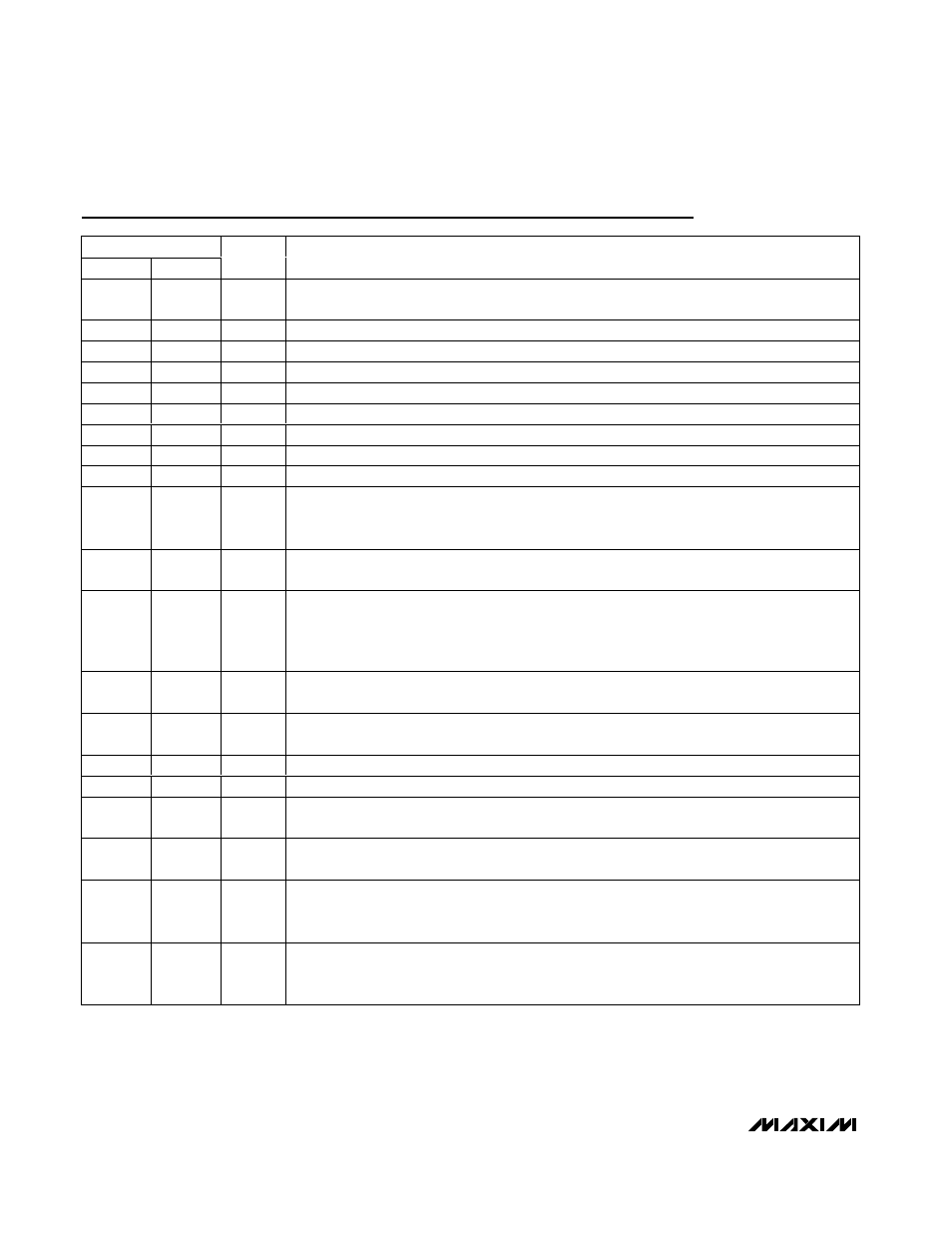

Pin Description

PIN

MAX1300 MAX1301

NAME

FUNCTION

1

2

AV

DD1

Analog Supply Voltage 1. Connect AV

DD1

to a +4.75V to +5.25V power-supply voltage. Bypass

AV

DD1

to AGND1 with a 0.1µF capacitor.

2

3

CH0

Analog Input Channel 0

3

4

CH1

Analog Input Channel 1

4

5

CH2

Analog Input Channel 2

5

6

CH3

Analog Input Channel 3

6

—

CH4

Analog Input Channel 4

7

—

CH5

Analog Input Channel 5

8

—

CH6

Analog Input Channel 6

9

—

CH7

Analog Input Channel 7

10

7

CS

Active-Low Chip-Select Input. When CS is low, data is clocked into the device from DIN on the

rising edge of SCLK. With CS low, data is clocked out of DOUT on the falling edge of SCLK.

When CS is high, activity on SCLK and DIN is ignored and DOUT is high impedance.

11

8

DIN

Serial Data Input. When CS is low, data is clocked in on the rising edge of SCLK. When CS is

high, transitions on DIN are ignored.

12

9

SSTRB

Serial-Strobe Output. When using the internal clock, SSTRB rising edge transitions indicate that

data is ready to be read from the device. When operating in external clock mode, SSTRB is

always low. SSTRB does not tri-state, regardless of the state of CS, and therefore requires

a dedicated I/O line.

13

10

SCLK

Serial Clock Input. When CS is low, transitions on SCLK clock data into DIN and out of DOUT.

When CS is high, transitions on SCLK are ignored.

14

11

DOUT

Serial Data Output. When CS is low, data is clocked out of DOUT with each falling SCLK

transition. When CS is high, DOUT is high impedance.

15

12

DGNDO

Digital I/O Ground. DGND, DGNDO, AGND3, AGND2, and AGND1 must be connected together.

16

13

DGND

Digital Ground. DGND, DGNDO, AGND3, AGND2, and AGND1 must be connected together.

17

14

DV

DDO

Digital I/O Supply Voltage Input. Connect DV

DDO

to a +2.7V to +5.25V power-supply voltage.

Bypass DV

DDO

to DGNDO with a 0.1µF capacitor.

18

15

DV

DD

Digital-Supply Voltage Input. Connect DV

DD

to a +4.75V to +5.25V power-supply voltage.

Bypass DV

DD

to DGND with a 0.1µF capacitor.

19

16

REFCAP

Bandgap-Voltage Bypass Node. For external reference operation, connect REFCAP to AV

DD

.

For internal reference operation, bypass REFCAP with a 0.01µF capacitor to AGND1

(V

REFCAP

≈ 4.096V).

20

17

REF

Reference-Buffer Output/ADC Reference Input. For external reference operation, apply an

external reference voltage from 3.800V to 4.136V to REF. For internal reference operation,

bypassing REF with a 1µF capacitor to AGND1 sets V

REF

= 4.096V ±1%.