Table 7. mode-control byte – Rainbow Electronics MAX1301 User Manual

Page 23

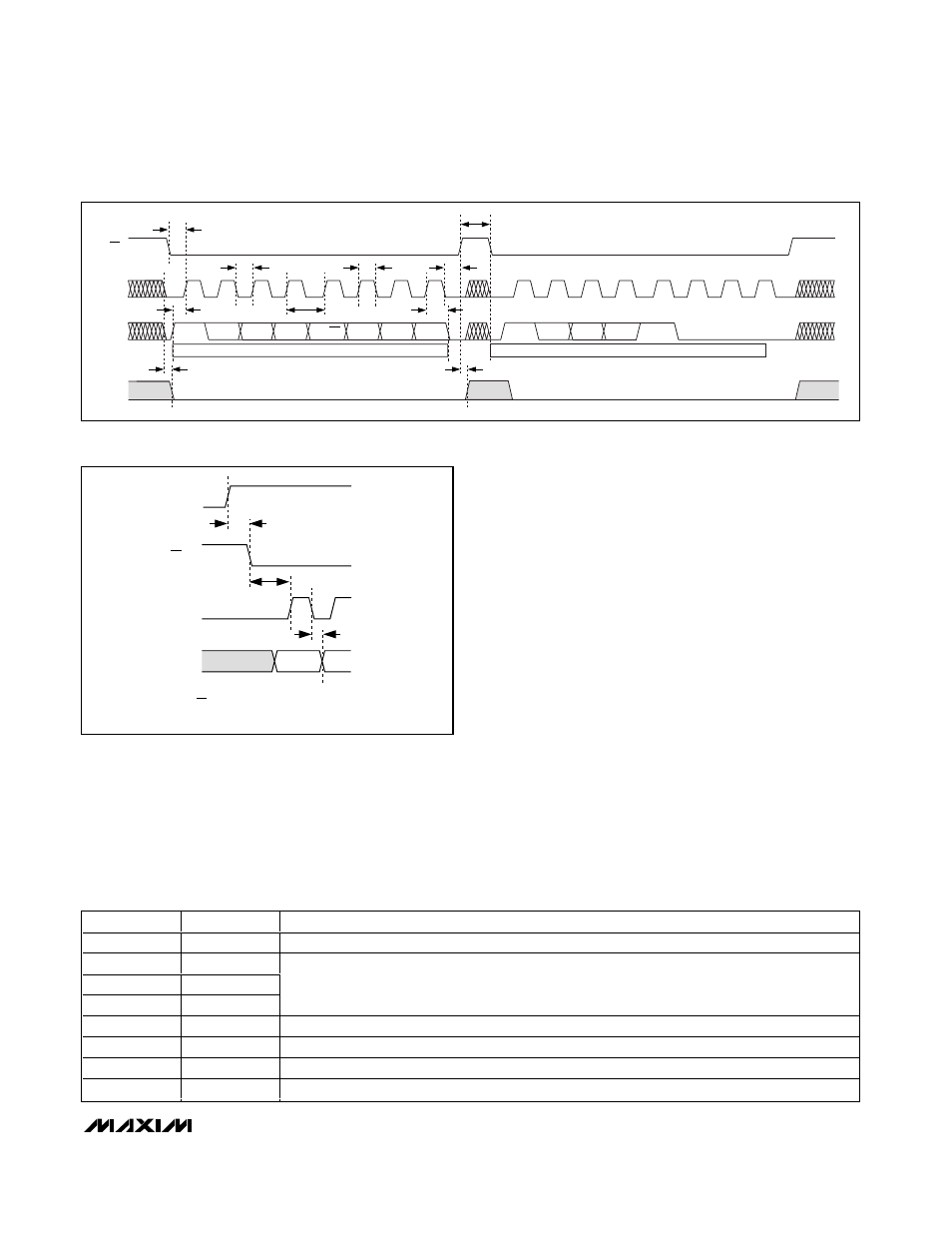

• User supplies one byte of SCLK, then drives CS

high to relieve processor load while the ADC

converts

• After SSTRB transitions high, the user supplies

two bytes of SCLK and reads data at DOUT

External Clock Mode (Mode 0)

The MAX1300/MAX1301’s fastest maximum throughput

rate is achieved operating in external clock mode.

SCLK controls both the acquisition and conversion of

the analog signal, facilitating precise control over when

the analog signal is captured. The analog input sam-

pling instant is at the falling edge of the 14th SCLK

(Figure 2).

Since SCLK drives the conversion in external clock

mode, the SCLK frequency should remain constant

while the conversion is clocked. The minimum SCLK

frequency prevents droop in the internal sampling

capacitor voltages during conversion.

SSTRB remains low in the external clock mode, and as a

result may be left unconnected if the MAX1300/

MAX1301 will always be used in the external clock mode.

MAX1300/MAX1301

8-/4-Channel, ±12V Multirange Inputs,

Serial 16-Bit ADCs

______________________________________________________________________________________

23

CS

SCLK

DIN

DOUT

1

8

START

SEL2

SEL1

SEL0

R2

R1

R0

DIF/SGL

t

CL

t

CP

t

CH

t

DV

t

CSS

t

DS

t

DH

t

CSH

t

CSPW

t

TR

1

8

START

M2

M1

M0

1

0

0

0

ANALOG INPUT CONFIGURATION BYTE

MODE CONTROL BYTE

HIGH

IMPEDANCE

HIGH

IMPEDANCE

HIGH

IMPEDANCE

Figure 15. Analog Input Configuration Byte and Mode-Control Byte Timing

CS

SCLK

DOUT

t

CSS

SSTRB

t

SSCS

MSB

t

DO

NOTE: SSTRB AND CS REMAIN LOW IN EXTERNAL CLOCK MODE (MODE 0).

HIGH

IMPEDANCE

Figure 16. DOUT and SSTRB Timing

Table 7. Mode-Control Byte

BIT NUMBER

BIT NAME

DESCRIPTION

7

START

Start Bit. The first logic 1 after CS goes low defines the beginning of the mode-control byte.

6

M2

5

M1

4

M0

Mode-Control Bits. M[2:0] select the mode of operation as shown in Table 8.

3

1

Bit 3 must be a logic 1 for the mode-control byte.

2

0

Bit 2 must be a logic 0 for the mode-control byte.

1

0

Bit 1 must be a logic 0 for the mode-control byte.

0

0

Bit 0 must be a logic 0 for the mode-control byte.