Detailed description – Rainbow Electronics MAX1421 User Manual

Page 10

MAX1421

12-Bit, 40Msps, +3.3V, Low-Power ADC

with Internal Reference

10

______________________________________________________________________________________

Detailed Description

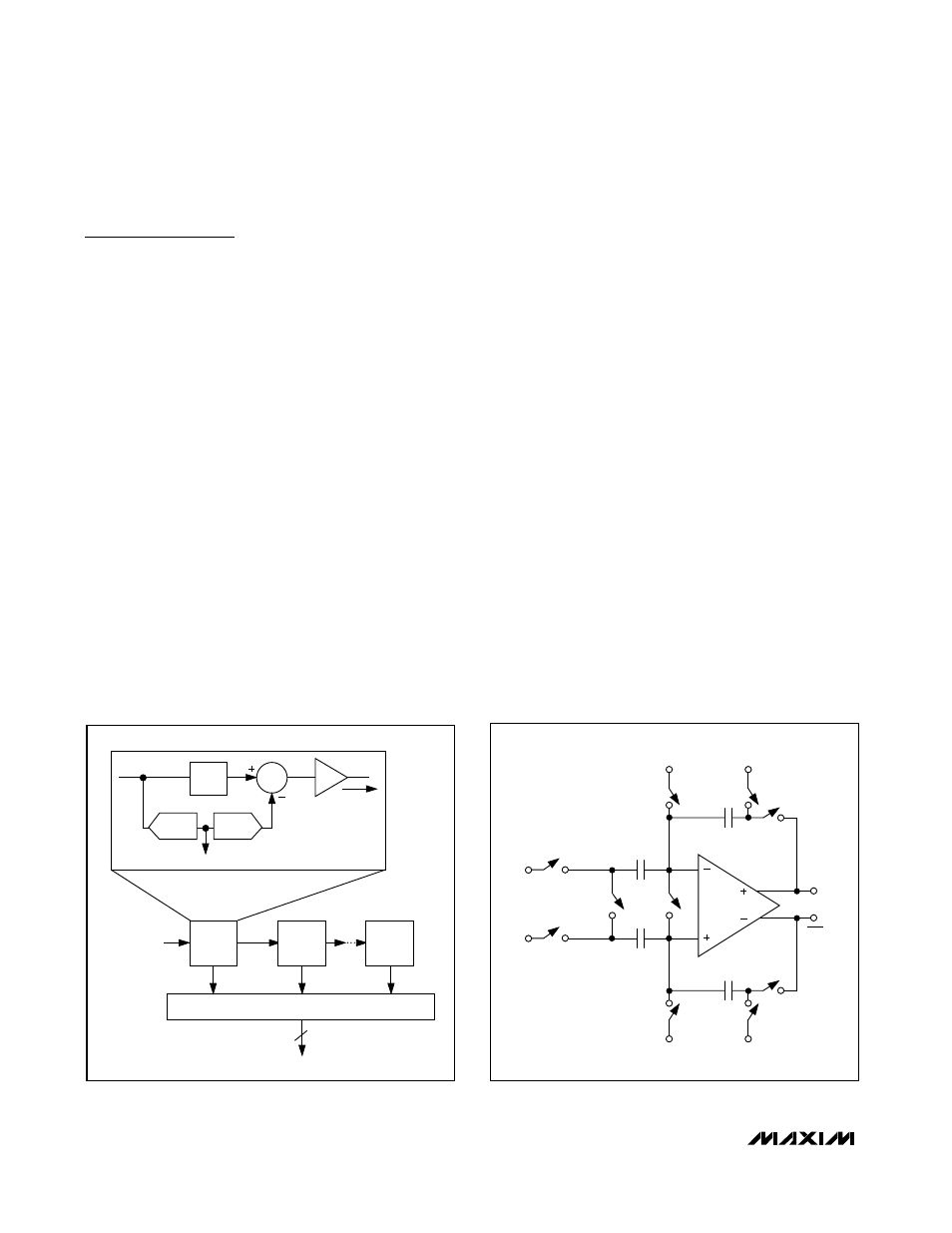

The MAX1421 uses a 12-stage, fully-differential, pipe-

lined architecture (Figure 1) that allows for high-speed

conversion while minimizing power consumption. Each

sample moves through a pipeline stage every half-

clock-cycle. Including the delay through the output latch,

the latency is seven clock cycles.

A 2-bit (2-comparator) flash ADC converts the held-

input voltage into a digital code. The following digital-to-

analog converter (DAC) converts the digitized result

back into an analog voltage, which is then subtracted

from the original held-input signal. The resulting error

signal is then multiplied by two, and the product is

passed along to the next pipeline stage. This process is

repeated until the signal has been processed by all 12

stages. Each stage provides a 1-bit resolution. Digital

error correction compensates for ADC comparator off-

sets in each pipeline stage and ensures no missing

codes.

Input Track-and-Hold Circuit

Figure 2 displays a simplified functional diagram of the

input T/H circuit in both track-and-hold modes. In track

mode, switches S1, S2a, S2b, S4a, S4b, S5a, and S5b

are closed. The fully differential circuit passes the input

signal to the two capacitors (C2a and C2b) through-

switches (S4a and S4b). Switches S2a and S2b set the

common mode for the transconductance amplifier

(OTA) input, and open simultaneously with S1, sam-

pling the input waveform. The resulting differential volt-

age is held on capacitors C2a and C2b. Switches S4a

and S4b are then opened before switches S3a and S3b,

connecting capacitors C1a and C1b to the output of the

amplifier, and switch S4c is closed. The OTA is used to

charge capacitors C1a and C1b to the same values

originally held on C2a and C2b. This value is then pre-

sented to the first-stage quantizer and isolates the

pipeline from the fast-changing input. The wide-input

bandwidth, T/H amplifier allows the MAX1421 to track

and sample/hold analog inputs of high frequencies

beyond Nyquist. The analog inputs INP and INN can be

driven either differentially or single-ended. Match the

impedance of INP and INN and set the common-mode

voltage to midsupply (AV

DD

/ 2) for optimum perfor-

mance.

Analog Input and Reference Configuration

The full-scale range of the MAX1421 is determined by

the internally generated voltage difference between

REFP (AV

DD

/ 2 + V

REFIN

/ 4) and REFN (AV

DD

/ 2 -

V

REFIN

/ 4). The MAX1421’s full-scale range is

adjustable through REFIN, which provides a high input

impedance for this purpose. REFP, CML (AV

DD

/ 2), and

REFN are internally buffered low impedance outputs.

T/H

V

OUT

x2

Σ

FLASH

ADC

DAC

2 BITS

MDAC

12

V

IN

V

IN

STAGE 1

STAGE 2

D11–D0

DIGITAL CORRECTION LOGIC

STAGE 12

TO NEXT

STAGE

Figure 1. Pipelined Architecture

S3b

S3a

CML

S5b

S2b

S5a

S1

OUT

OUT

C2a

C2b

S4c

S4a

S4b

C1b

C1a

INTERNAL

BIAS

OTA

INTERNAL

BIAS

CML

S2a

Figure 2. Internal Track-and-Hold Circuit