Electrical characteristics (continued) – Rainbow Electronics MAX1127 User Manual

Page 5

MAX1127

Quad, 12-Bit, 65Msps, 1.8V ADC with

Serial LVDS Outputs

_______________________________________________________________________________________

5

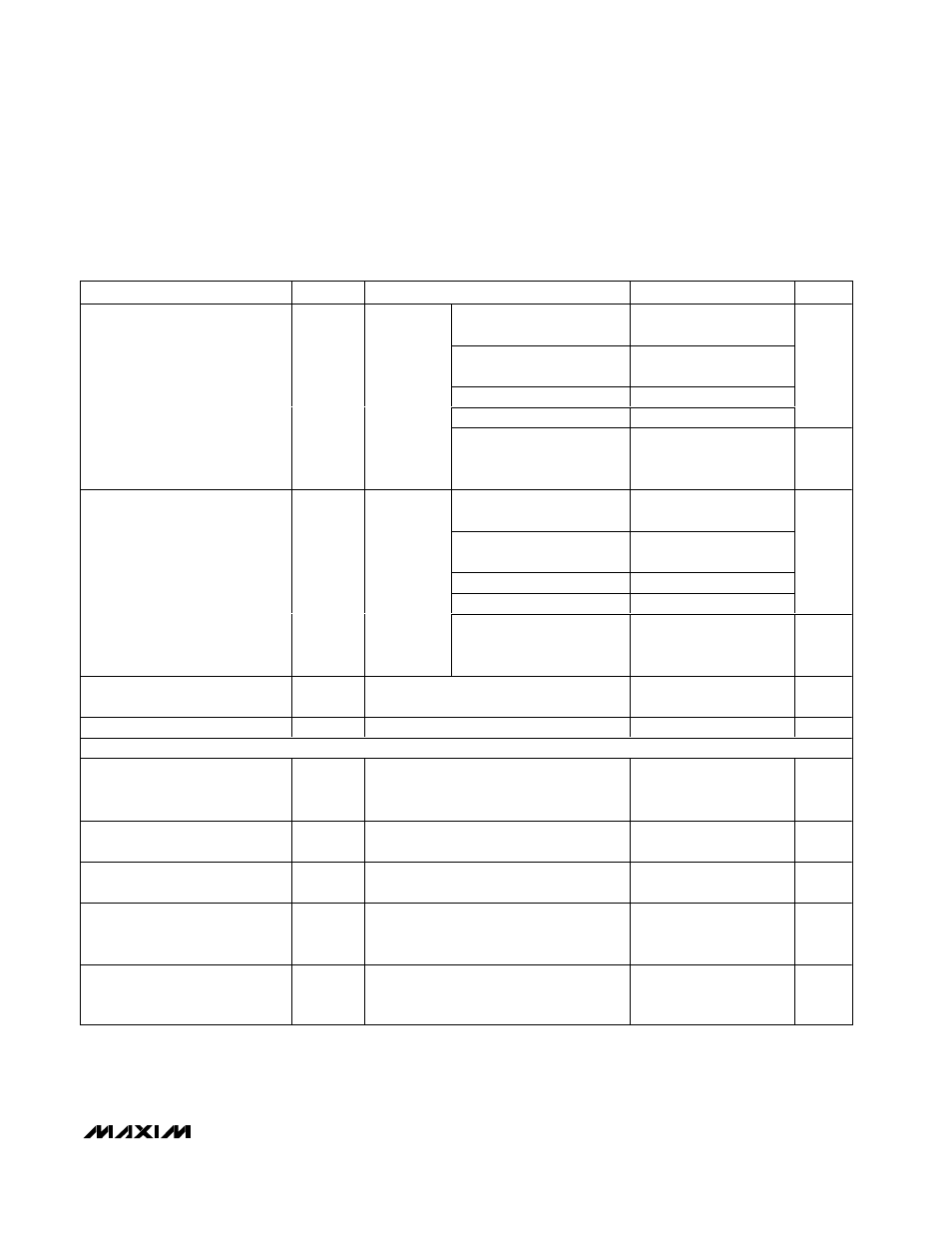

ELECTRICAL CHARACTERISTICS (continued)

(AV

DD

= 1.8V, OV

DD

= 1.8V, CV

DD

= 1.8V, GND = 0, external V

REFIO

= 1.24V, INTREF = AV

DD

, C

REFIO

to GND = 0.1µF,

f

CLK

= 65MHz (50% duty cycle), DT = 0, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at T

A

= +25°C.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

PDALL = 0, all channels

active

257

295

PDALL = 0, all channels

active, DT = 1

257

PDALL = 0, 1 channel active

82

PDALL = 0, PD[3:0] = 1111

23

mA

AV

DD

Supply Current

I

AVDD

f

IN

=

19.3MHz at

-0.5dBFS

PDALL = 1, global power

down, PD[3:0] =1111, no

clock input

300

µA

PDALL = 0, all channels

active

56

65

PDALL = 0, all channels

active, DT = 1

72

PDALL = 0, 1 channel active

42

PDALL = 0, PD[3:0] = 1111

37

mA

OV

DD

Supply Current

I

OVDD

f

IN

=

19.3MHz at

-0.5dBFS

PDALL = 1, global power-

down, PD[3:0] =1111, no

clock input

375

µA

CV

DD

Supply Current

I

CVDD

CV

DD

is used only to bias ESD-protection

diodes on CLK input, Figure 2

0

mA

Power Dissipation

P

DISS

f

IN

= 19.3MHz at -0.5dBFS

563

648

mW

TIMING CHARACTERISTICS

(Note 6)

Data Valid to CLKOUT Rise/Fall

t

OD

f

CLK

= 65MHz, Figure 5 (Notes 6 and 7)

(t

SAMPLE

/

24)

- 0.15

t

SAMPLE

/

24

(t

SAMPLE

/

24)

+ 0.15

ns

CLKOUT Output Width High

t

CH

Figure 5

t

S AMP LE

/

12

ns

CLKOUT Output Width Low

t

CL

Figure 5

t

S AMP LE

/

12

ns

FRAME Rise to CLKOUT Rise

t

CF

Figure 4 (Note 7)

(t

SAMPLE

/

24)

- 0.15

t

SAMPLE

/

24

( t

SAMPLE

/

24)

+ 0.15

ns

Sample CLK Rise to Frame Rise

t

SF

Figure 4 (Notes 7 and 8)

(t

SAMPLE

/

2)

+0.9

(t

SAMPLE

/

2)

+1.3

(t

SAMPLE

/

2)

+1.7

ns