Pin description (continued) – Rainbow Electronics MAX1127 User Manual

Page 15

MAX1127

Quad, 12-Bit, 65Msps, 1.8V ADC with

Serial LVDS Outputs

______________________________________________________________________________________

15

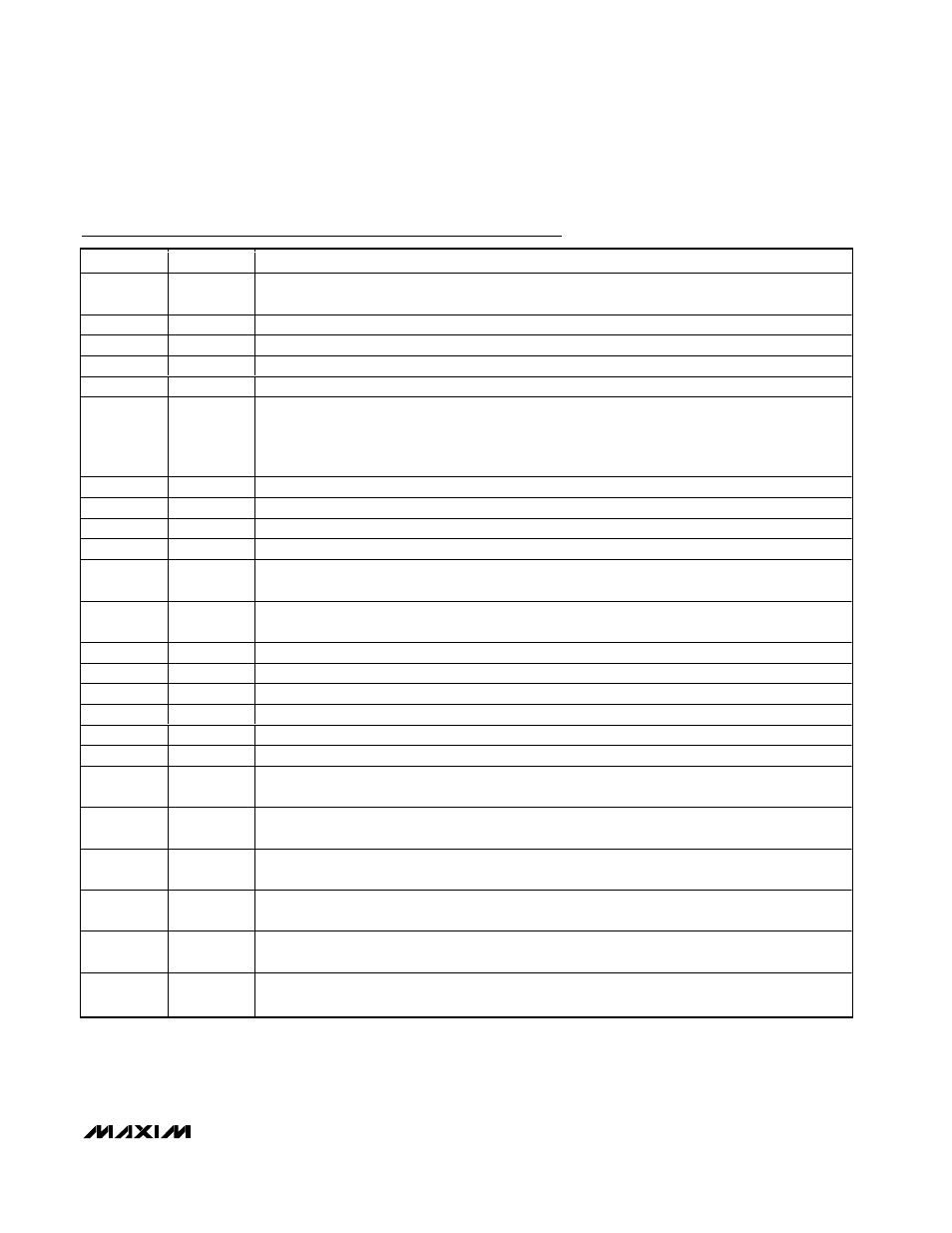

PIN

NAME

FUNCTION

29

SLVS/LVDS

Differential Output Signal Format Select Input. Drive SLVS/LVDS high to select SLVS outputs. Drive

SLVS/LVDS low to select LVDS outputs.

30

PLL0

PLL Control Input 0. PLL0 is reserved for factory testing only and must always be connected to GND.

31

PLL1

PLL Control Input 1. PLL1 is reserved for factory testing only and must always be connected to GND.

32

PLL2

PLL Control Input 2. See Table 1 for details.

33

PLL3

PLL Control Input 3. See Table 1 for details.

34, 37, 40,

43, 46, 49,

52

OV

DD

Output-Driver Power Input. Connect OV

DD

to a 1.7V to 1.9V power supply. Bypass each OV

DD

to

GND with a 0.1µF capacitor as close to the device as possible. Bypass the OV

DD

power plane to the

GND ground plane with a bulk

≥

2.2µF capacitor as close to the device as possible. Connect all OV

DD

pins to the same potential.

35

OUT3N

Channel 3 Negative LVDS/SLVS Output

36

OUT3P

Channel 3 Positive LVDS/SLVS Output

38

OUT2N

Channel 2 Negative LVDS/SLVS Output

39

OUT2P

Channel 2 Positive LVDS/SLVS Output

41

FRAMEN

Negative Frame Alignment LVDS/SLVS Output. A rising edge on the differential FRAME output aligns

to a valid D0 in the output data stream.

42

FRAMEP

Positive Frame Alignment LVDS/SLVS Output. A rising edge on the differential FRAME output aligns to

a valid D0 in the output data stream.

44

CLKOUTN

Negative LVDS/SLVS Serial Clock Output

45

CLKOUTP

Positive LVDS/SLVS Serial Clock Output

47

OUT1N

Channel 1 Negative LVDS/SLVS Output

48

OUT1P

Channel 1 Positive LVDS/SLVS Output

50

OUT0N

Channel 0 Negative LVDS/SLVS Output

51

OUT0P

Channel 0 Positive LVDS/SLVS Output

53

PD0

Channel 0 Power-Down Input. Drive PD0 high to power-down channel 0. Drive PD0 low for normal

operation.

54

PD1

Channel 1 Power-Down Input. Drive PD1 high to power-down channel 1. Drive PD1 low for normal

operation.

55

PD2

Channel 2 Power-Down Input. Drive PD2 high to power-down channel 2. Drive PD2 low for normal

operation.

56

PD3

Channel 3 Power-Down Input. Drive PD3 high to power-down channel 3. Drive PD3 low for normal

operation.

57

PDALL

Global Power-Down Input. Drive PDALL high to power-down all channels and reference. Drive PDALL

low for normal operation.

63

T/B

Output Format Select Input. Drive T/B high to select binary output format. Drive T/B low to select two’s

complement output format.

Pin Description (continued)