Fuse bits, Atmega32(l) – Rainbow Electronics ATmega32L User Manual

Page 255

255

ATmega32(L)

2503C–AVR–10/02

Notes:

1. Program the fuse bits before programming the Lock bits.

2. “1” means unprogrammed, “0” means programmed

Fuse Bits

The ATmega32 has two fuse bytes. Table 105 and Table 106 describe briefly the func-

tionality of all the fuses and how they are mapped into the fuse bytes. Note that the

fuses are read as logical zero, “0”, if they are programmed.

Notes:

1. The SPIEN Fuse is not accessible in SPI Serial Programming mode.

2. The CKOPT Fuse functionality depends on the setting of the CKSEL bits. See See

“Clock Sources” on page 23. for details.

3. The default value of BOOTSZ1..0 results in maximum Boot Size. See Table 100 on

page 253.

4. Never ship a product with the OCDEN Fuse programmed regardless of the setting of

Lock bits and the JTAGEN Fuse. A programmed OCDEN Fuse enables some parts

of the clock system to be running in all sleep modes. This may increase the power

consumption.

1

1

1

No restrictions for SPM or LPM accessing the Boot Loader

section.

2

1

0

SPM is not allowed to write to the Boot Loader section.

3

0

0

SPM is not allowed to write to the Boot Loader section,

and LPM executing from the Application section is not

allowed to read from the Boot Loader section. If interrupt

vectors are placed in the Application section, interrupts

are disabled while executing from the Boot Loader

section.

4

0

1

LPM executing from the Application section is not allowed

to read from the Boot Loader section. If interrupt vectors

are placed in the Application section, interrupts are

disabled while executing from the Boot Loader section.

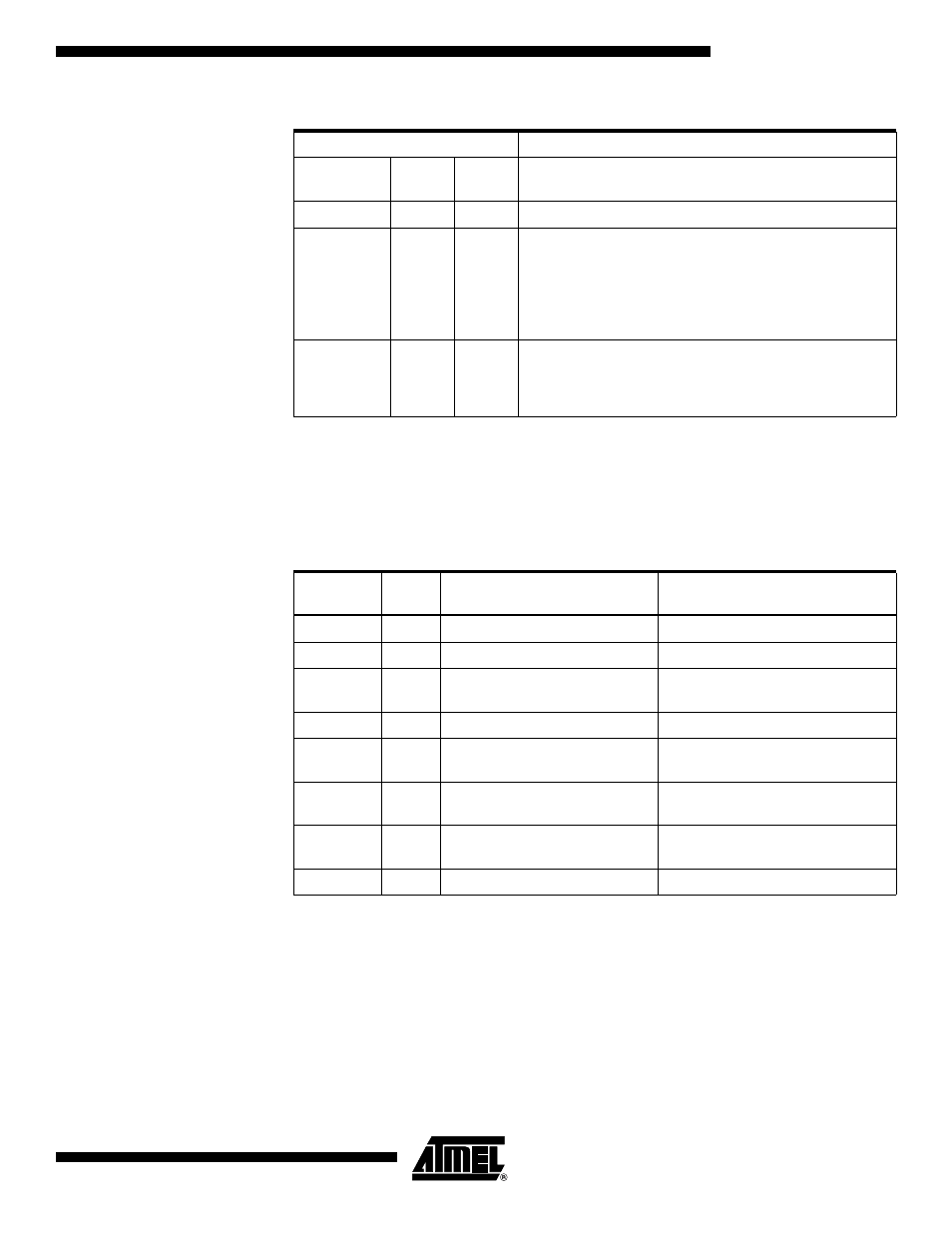

Table 104. Lock Bit Protection Modes (Continued)

Memory Lock Bits

(2)

Protection Type

Table 105. Fuse High Byte

Fuse High

Byte

Bit

No.

Description

Default Value

OCDEN

(4)

7

Enable OCD

1 (unprogrammed, OCD disabled)

JTAGEN

6

Enable JTAG

0 (programmed, JTAG enabled)

SPIEN

(1)

5

Enable SPI Serial Program and

Data Downloading

0 (programmed, SPI prog. enabled)

CKOPT

(2)

4

Oscillator options

1 (unprogrammed)

EESAVE

3

EEPROM memory is preserved

through the Chip Erase

1 (unprogrammed, EEPROM not

preserved)

BOOTSZ1

2

Select Boot Size (see Table 100

for details)

0 (programmed)

(3)

BOOTSZ0

1

Select Boot Size (see Table 100

for details)

0 (programmed)

(3)

BOOTRST

0

Select reset vector

1 (unprogrammed)