Interrupts – Rainbow Electronics DS89C450 User Manual

Page 36

DS89C430/DS89C440/DS89C450 Ultra-High-Speed Flash Microcontrollers

36 of 48

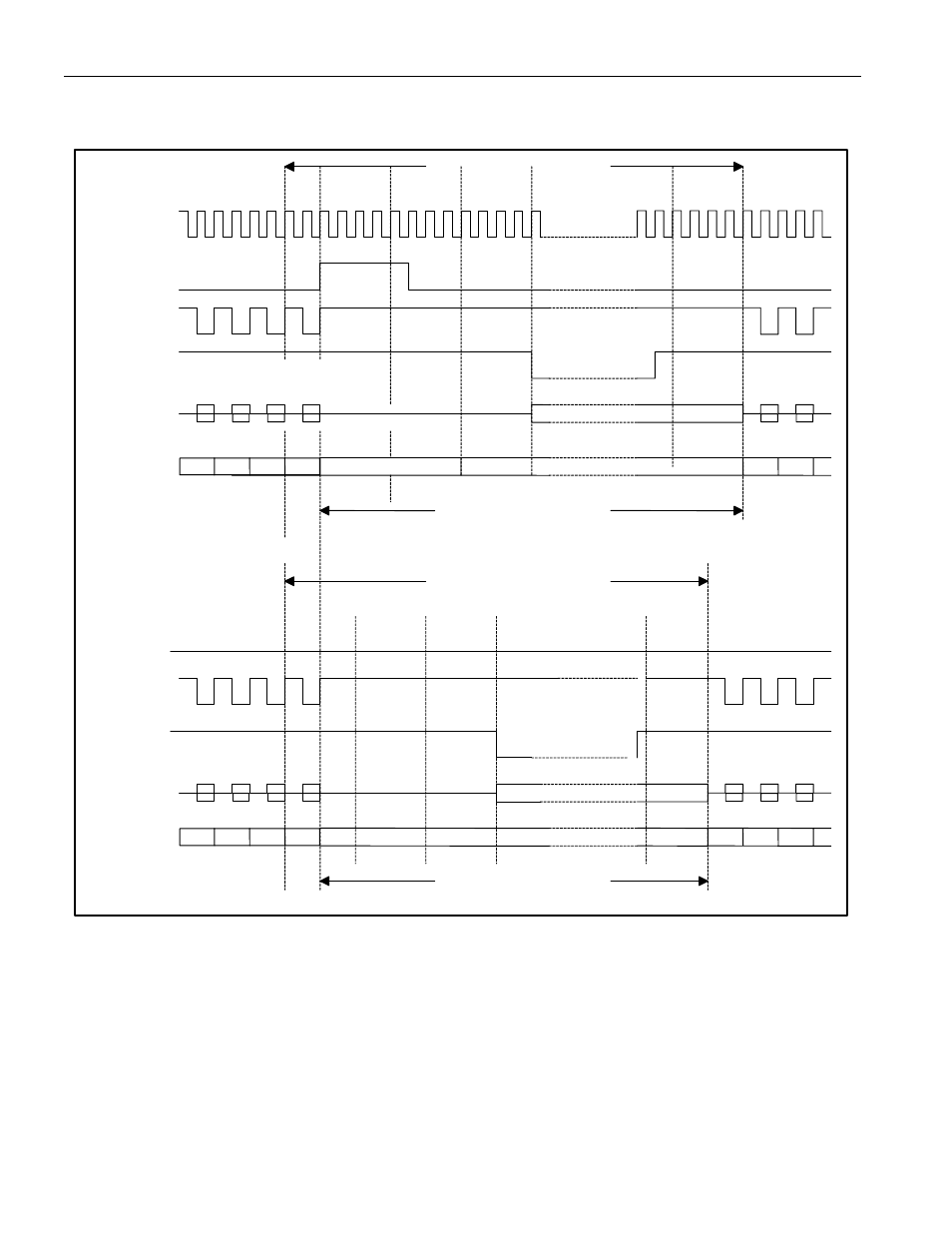

Figure 13. Page Mode 1, External Data Memory Access

(PAGES = 01, Stretch = 4, CD = 10)

ALE

PSEN

Port 0

Port 2

ALE

PSEN

Port 0

Port 2

RD/WR

XTAL1

Inst

Inst

Inst

Inst

Inst

MSB

LSB

LSB

LSB

LSB

LSB

LSB LSB

Inst

Data

Memory Access (Stretch = 4)

MOVX Instruction (Page miss)

1st

Cycle

2nd

Cycle

3rd

Cycle

4th

Cycle

9th

Cycle

MOVX

Instruction

Fetch

LSB

LSB LSB

Inst

Inst Inst

MOVX Instruction (Page hit)

Memory Access (Stretch = 4)

MOVX

Instruction

Fetch

1st

Cycle

2nd

Cycle

3rd

Cycle

4th

Cycle

5th

Cycle

9th

Cycle

LSB

LSB

LSB

LSB

Inst

Inst

Inst

Inst

RD/WR

Data

LSB

Interrupts

The DS89C430 provides 13 interrupt sources. All interrupts, with the exception of the power fail, are controlled by a

series combination of individual enable bits and a global enable (EA) in the interrupt-enable register (IE.7). Setting

EA to a logic 1 allows individual interrupts to be enabled. Setting EA to a logic 0 disables all interrupts regardless of

the individual interrupt-enable settings. The power-fail interrupt is controlled by its individual enable only.

The interrupt enables and priorities are functionally identical to those of the 80C52, except that the DS89C430

supports five levels of interrupt priorities instead of the original two.