Table 4. in-application programming commands – Rainbow Electronics DS89C450 User Manual

Page 24

DS89C430/DS89C440/DS89C450 Ultra-High-Speed Flash Microcontrollers

24 of 48

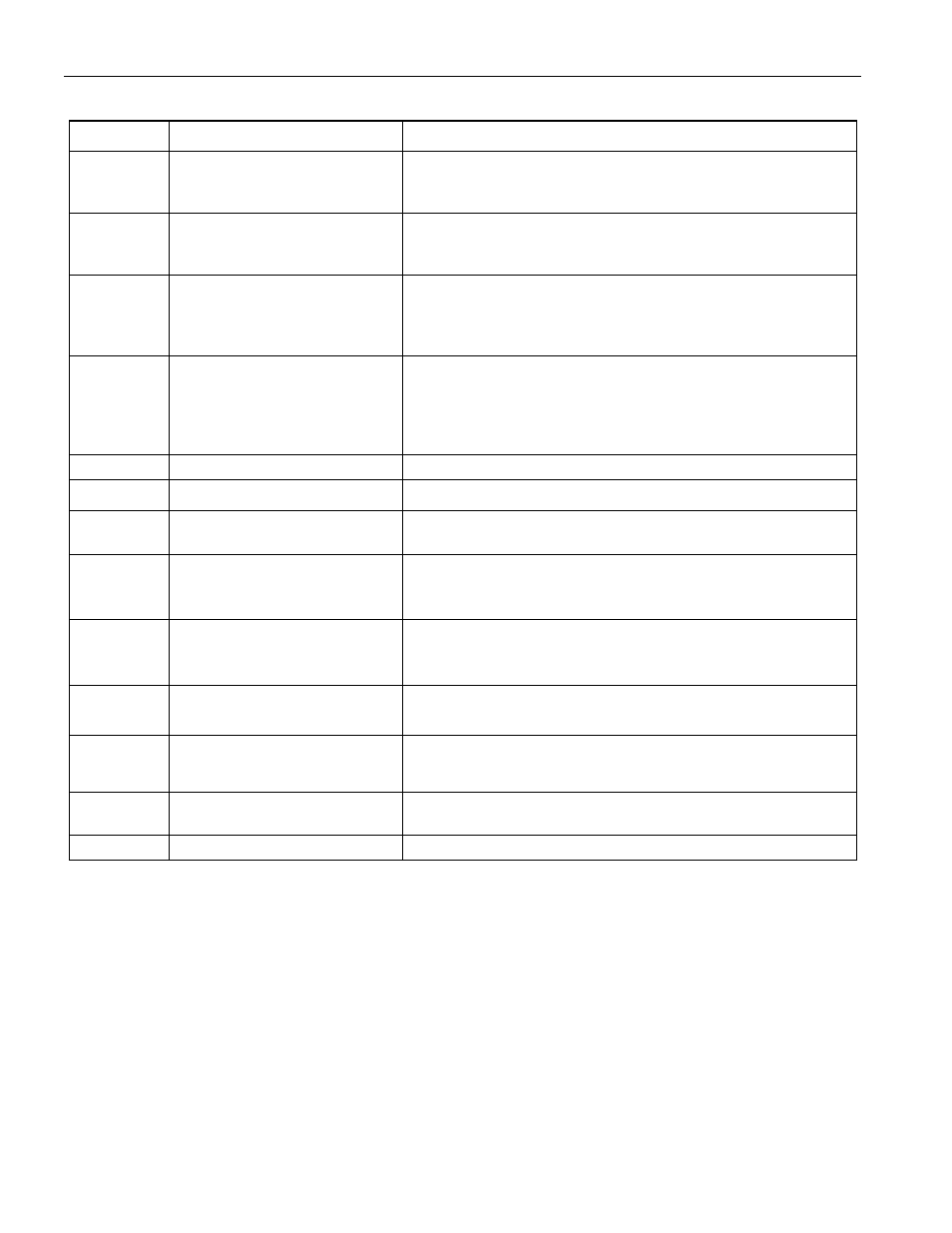

Table 4. In-Application Programming Commands

FC3:FC0 COMMAND

OPERATION

0000 Read

Mode

Default state. All flash blocks are in read mode. Note: The upper bank

of flash memory is inaccessible for execution unless the FC3:0 bits are

in the read mode (0000b) state.

0001

Verify Option Control Register

Read data from the option control register. Data is available in the

FDATA at the end of the following machine cycle. FDATA.3 is the logic

value of the watchdog POR default setting.

0010

Verify Security Block

Read a byte of data from the security block. After the address byte is

written to the FDATA, data is available in the FDATA at the end of the

following machine cycle. (Lock bits are addressed at 40h and

FDATA.5:3 are the logic value of LB1, LB2 and LB3, respectively.)

0011

Verify Upper Program

Memory Bank

Read a byte of data from upper flash memory bank (address range

from 2000h to 3FFFh). The first and second byte writes to the FDATA

are the upper and lower byte of the address. Data is available in the

FDATA at the end of the following machine cycle after the second

address byte is written.

0100

Reserved for Future Use

This command should not be modified by user programs.

1000

Reserved for Future Use

This command should not be modified by user programs.

1001

Write Option Control Register

Write to the option control register as data is written to FDATA. Bit 3 of

the data byte represents the watchdog POR default setting.

1010

Write Security Block

Write a byte of data to the security block at a selected locations

addressed by the first byte write to the FDATA. The second write to the

FDATA is the data byte. (Lock bits are addressed at 40h and the

FDATA 5:3 represents lock bits LB3, LB2, and LB1, respectively.)

1011

Write Upper Program

Memory Bank

Write a byte of code to the upper flash memory bank (address range

from 2000h to 3FFFh). The first and second byte writes to the FDATA

are the upper byte and the lower byte of the address. The third write to

the FDATA is the data byte.

1100

Erase Option Control Register

Erase the option control register. The contents of this register are

returned to FFh. This operation disables the watchdog reset function on

power-up.

1101

Erase Security Block

Erase the security flash block that contains the 64-byte encryption array

and the lock bits. The content of every memory location is turned into

FFh.

1110

Erase Upper Program

Memory Bank

Erase the upper bank of flash memory bank. The contents of every

memory location are returned to FFh.

1111

System Reset

This command is used to cause a system reset.

The flash command bits are cleared to 0 on all forms of reset, and it is important for the user software to clear

these bits to 0 to return the flash memory to read mode from erase/program operation. This setting is a “no

operation” condition for the MMU, which allows the processor to return to its normal execution. Note that the busy

and error flags have no function in normal flash-read mode.

The FCNTL SFR can only be written using timed access. This procedure provides protection against inadvertent

erase/program operation on the flash memory. Any command written to the FCNTL during a flash operation is

ignored (FBUSY = 0). To ensure data integrity, an erase command sequence should be reinitiated if an erase or

program operation is interrupted by a reset.