Table 5. parallel programming instruction set, Data pointer increment/decrement and options – Rainbow Electronics DS89C450 User Manual

Page 26

DS89C430/DS89C440/DS89C450 Ultra-High-Speed Flash Microcontrollers

26 of 48

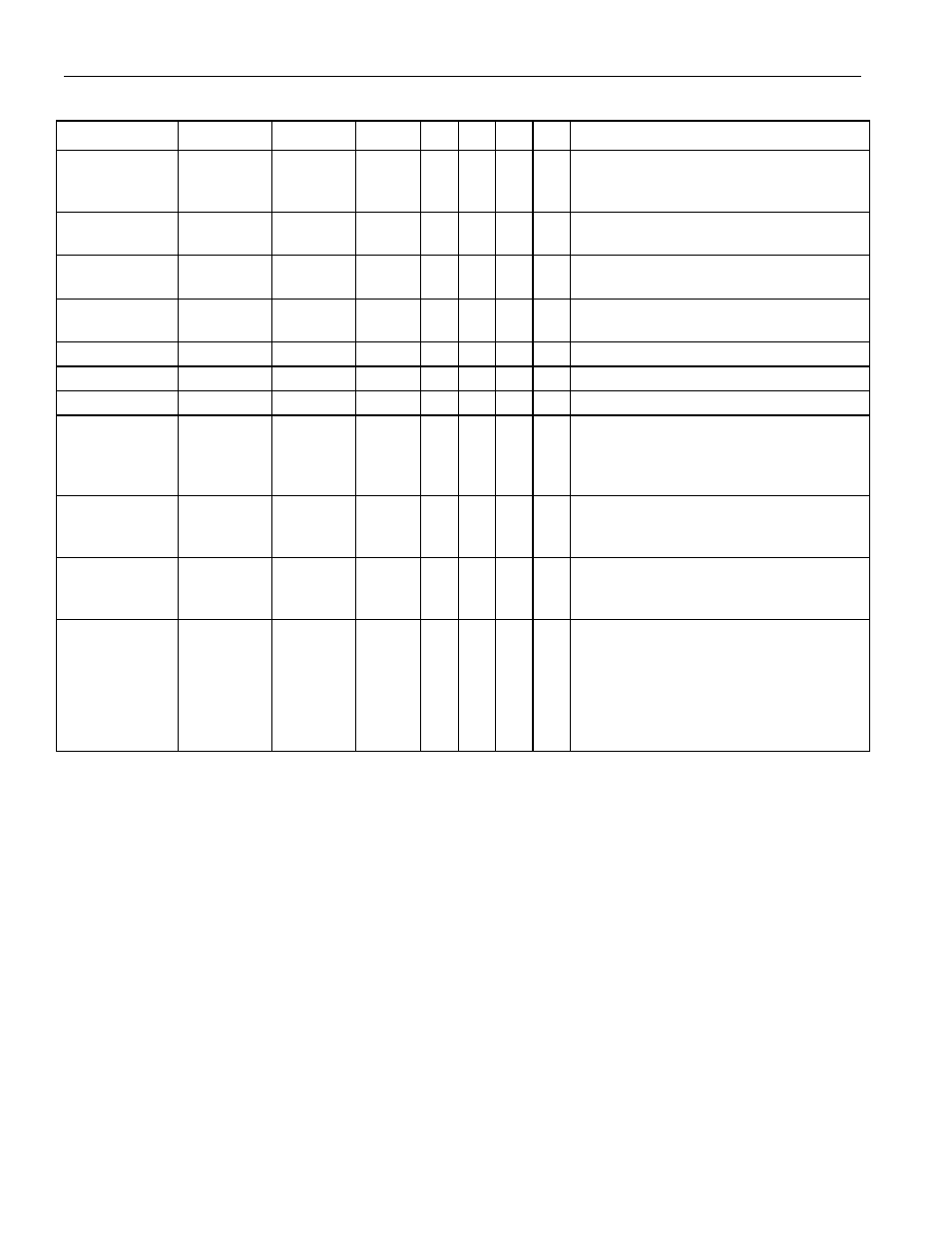

Table 5. Parallel Programming Instruction Set

INSTRUCTION P2.5:0,

P1.7:0 P0.7:0

PROG P2.6 P2.7 P3.6 P3.7

OPERATION

Mass Erase

Don’t care

Don’t care

PL

1

H L L L

Mass erase the program memory and the

security block. The contents of every memory

location is returned to FFh.

Write Program

Memory

ADDR DIN PL

2

L H H H Program

the

program

memory

Read Program

Memory

ADDR DOUT H

3

L

L

H

H

Verify the program memory

Write Encryption

Array

ADDR DIN PL

2

L H L H

Program

the

encryption

array

Write LB1

Don’t care

Don’t care

PL

2

H

H

H

H

Program LB1 to logic 0

Write LB2

Don’t care

Don’t care

PL

2

H

H

L

L

Program LB2 and LB1 to 00b

Write LB3

Don’t care

Don’t care

PL

2

H

L

H

L

Program LB3, LB2, and LB1 to 000b

Read Lock Bits

Don’t care

DOUT

H

3

L L L H

Verify the lock bits. The lock bits are at

address 40h and the three LSBs of the DOUT

are the logic value of the lock bits LB3, LB2,

and LB1, respectively.

Write Option

Control Register

Don’t care

DIN

PL

4

L H L L

Program the option control register. Bit 3 of

the DIN represents the watchdog POR default

setting.

Erase Option

Control Register

Don’t care

Don’t care

PL

4

H L L H

Erase the option control register. This

operation disables the watchdog reset

function on power-up.

Read Address

30, 31, 60, FC

ADDR DOUT H

3

L L L L

30h = Manufacturer ID

31h = Device ID

60h = Device extension

FCh = Verify the option control register. Bit 3

of the DOUT is the logic value of the

watchdog POR .

Note 1: Mass erase requires an active-low

PROG pulse width of 828ms.

Note 2: The byte program requires an active-low

PROG pulse width of 100ms (max).

Note 3:

PROG is weakly pulled to a high internally.

Note 4: The erase-option control register requires an active-low

PROG pulse width of 828ms.

On-Chip MOVX Data Memory

On-chip data memory is provided by the 1kB SRAM and occupies addresses 0000h–03FFh. The internal data

memory is disabled after a power-on reset, and any MOVX instruction directs the data memory access to external

data memory. To enable the internal data memory, software must configure the data memory enable bits DME1

and DME0 (PMR.1–0). Refer to the SFR Bit Descriptions section of the Ultra-High-Speed Flash Microcontroller

User’s Guide for data memory configurations. Once enabled, MOVX instructions with addresses inside the 1kB

range access the on-chip data memory, and addresses exceeding the 1kB range automatically access external

data memory. An internal data memory cycle spans only one system clock period to support fast internal execution.

Data Pointer Increment/Decrement and Options

The DS89C430 incorporates a hardware feature to assist applications that require data pointer increment/

decrement. Data pointer increment/decrement bits ID0 and ID1 (DPS.6 and DPS.7) define how the INC DPTR

instruction functions in relation to the active DPTR (selected by the SEL bit). Setting ID0 = 1 and SEL = 0 enables

the decrement operation for DPTR, and execution of the INC DPTR instruction decrements the DPTR contents

by 1. Similarly, setting ID1 = 1 and SEL = 1 enables the decrement operation for DPTR1, and execution of the INC