Program memory lock bits, Programming the flash, At89c51rc – Rainbow Electronics AT89C51RC User Manual

Page 15

AT89C51RC

15

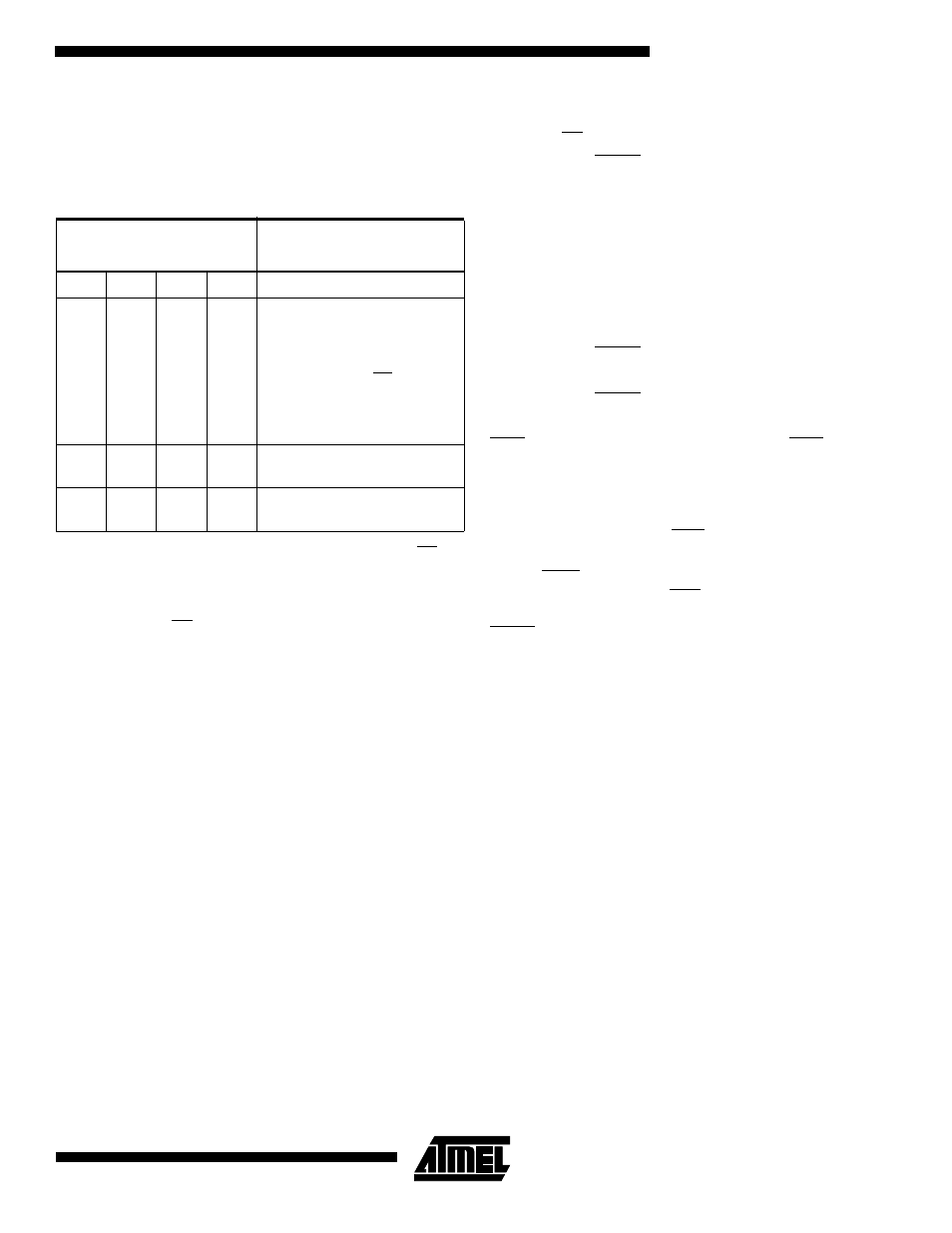

Program Memory Lock Bits

The AT89C51RC has three lock bits that can be left unpro-

grammed (U) or can be programmed (P) to obtain the addi-

tional features listed in the following table.

When lock bit 1 is programmed, the logic level at the EA pin

is sampled and latched during reset. If the device is pow-

ered up without a reset, the latch initializes to a random

value and holds that value until reset is activated. The

latched value of EA must agree with the current logic level

at that pin in order for the device to function properly.

Programming the Flash

The AT89C51RC is shipped with the on-chip Flash mem-

ory array ready to be programmed. The programming inter-

face needs a high-voltage (12-volt) program enable signal

and is compatible with conventional third-party Flash or

EPROM programmers.

The AT89C51RC code memory array is programmed byte-

by-byte.

Programming Algorithm: Before programming the

AT89C51RC, the address, data, and control signals should

be set up according to the Flash programming mode table

and Figures 10 and 11. To program the AT89C51RC, take

the following steps:

1.

Input the desired memory location on the address

lines.

2.

Input the appropriate data byte on the data lines.

3.

Activate the correct combination of control signals.

4.

Raise EA/V

PP

to 12V.

5.

Pulse ALE/PROG once to program a byte in the

Flash array or the lock bits. The byte-write cycle is

self-timed and typically takes no more than 50 µs.

Repeat steps 1 through 5, changing the address

and data for the entire array or until the end of the

object file is reached.

Chip Erase Sequence: Before the AT89C51RC can be

reprogrammed, a Chip Erase operation needs to be per-

formed. To erase the contents of the AT89C51RC, follow

this sequence:

1.

Pulse ALE/PROG once and wait for 150 ms.

2.

Power the device down and up again.

3.

Pulse ALE/PROG once again and wait for 150 ms.

4.

Power the device down and up again.

Data Polling: The AT89C51RC features Data Polling to

indicate the end of a write cycle. During a write cycle, an

attempted read of the last byte written will result in the com-

plement of the written data on P0.7. Once the write cycle

has been completed, true data is valid on all outputs, and

the next cycle may begin. Data Polling may begin any time

after a write cycle has been initiated.

Ready/Busy: The progress of byte programming can also

be monitored by the RDY/BSY output signal. P3.0 is pulled

low after ALE goes high during programming to indicate

BUSY. P3.0 is pulled high again when programming is

done to indicate READY.

Program Verify: If lock bits LB1 and LB2 have not been

programmed, the programmed code data can be read back

via the address and data lines for verification. The lock bits

cannot be verified directly. Verification of the lock bits is

achieved by observing that their features are enabled.

Reading the Signature Bytes: The signature bytes are

read by the same procedure as a normal verification of

locations 000H, 100H, and 200H, except that P3.6 and

P3.7 must be pulled to a logic low. The values returned are

as follows:

(000H) = 1EH indicates manufactured by Atmel

(100H) = 51H

(200H) = 07H indicates 89C51RC

Table 8. Lock Bit Protection Modes

Program Lock Bits

LB1

LB2

LB3

Protection Type

1

U

U

U

No program lock features

2

P

U

U

MOVC instructions executed

from external program

memory are disabled from

fetching code bytes from

internal memory, EA is

sampled and latched on reset,

and further programming of

the Flash memory is disabled

3

P

P

U

Same as mode 2, but verify is

also disabled

4

P

P

P

Same as mode 3, but external

execution is also disabled