Electrical characteristics (continued) – Rainbow Electronics MAX5974D User Manual

Page 4

MAX5974A/MAX5974B/MAX5974C/MAX5974D

Active-Clamped, Spread-Spectrum,

Current-Mode PWM Controllers

4

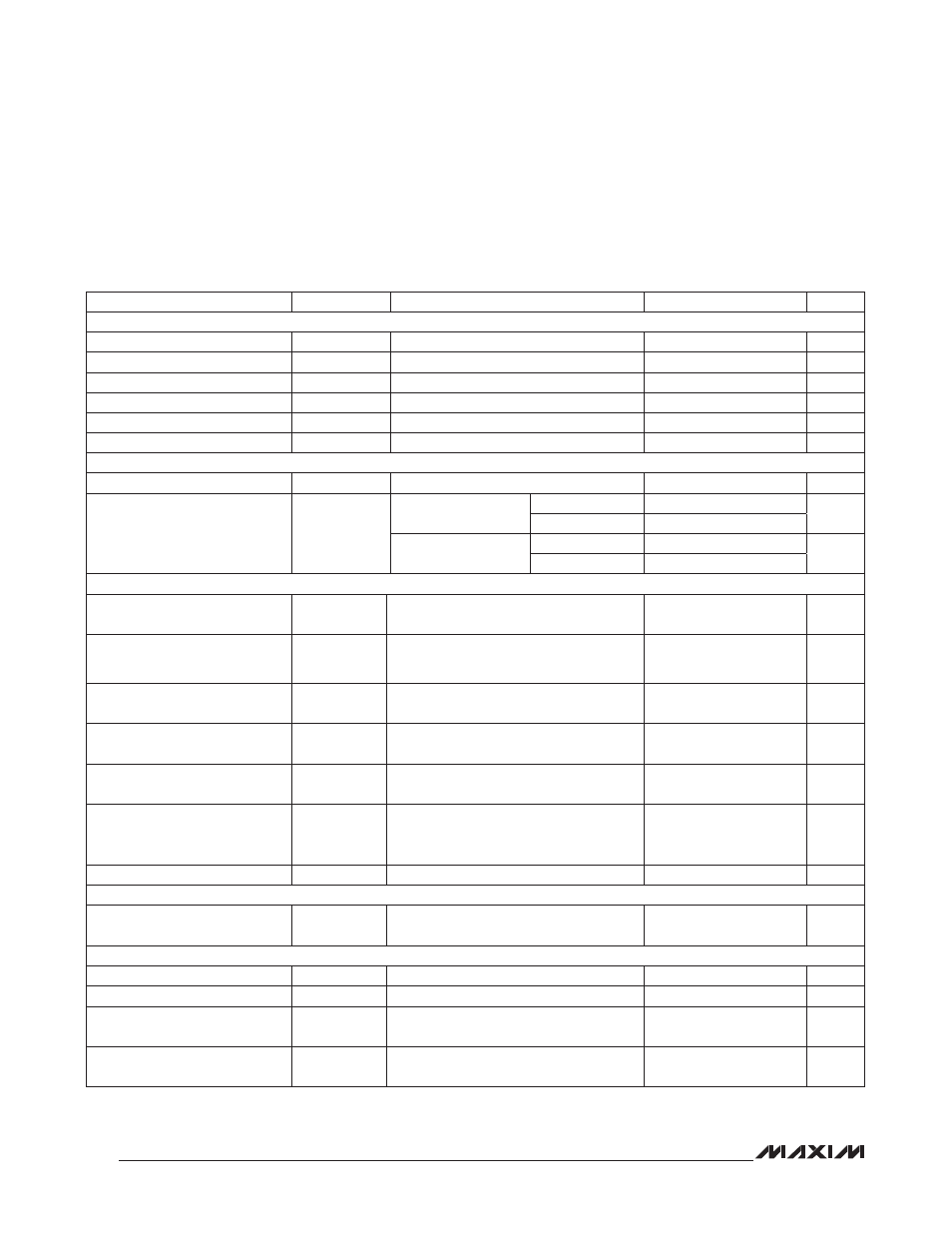

ELECTRICAL CHARACTERISTICS (continued)

(V

IN

= 12V (for MAX5974A/MAX5974C, bring V

IN

up to 21V for startup), V

CS

= V

CSSC

= V

DITHER/SYNC

= V

FB

= V

FFB

= V

DCLMP

=

V

GND

, V

EN

= +2V, NDRV = AUXDRV = SS = COMP = unconnected, R

RT

= 34.8kI, R

DT

= 25kI, C

IN

= 1FF, T

A

= -40NC to +85NC,

unless otherwise noted. Typical values are at T

A

= +25NC.) (Note 2)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

AUXDRV DRIVER

Pulldown Impedance

R

AUX-N

I

AUXDRV

(sinking) = 50mA

4.3

7.7

I

Pullup Impedance

R

AUX-P

I

AUXDRV

(sourcing) = 25mA

10.6

18.9

I

Peak Sink Current

0.5

A

Peak Source Current

0.3

A

Fall Time

t

AUX-F

C

AUXDRV

= 1nF

24

ns

Rise Time

t

AUX-R

C

AUXDRV

= 1nF

45

ns

DEAD-TIME PROGRAMMING (DT)

DT Bias Voltage

V

DT

1.215

V

NDRV to AUXDRV Delay

(Dead Time)

t

DT

From NDRV falling

to AUXDRV falling

R

DT

= 10kI

40

ns

R

DT

= 100kI

300

350

410

AUXDRV rising to

NDRV rising

R

DT

= 10kI

40

ns

R

DT

= 100kI

310

360

420

CURRENT-LIMIT COMPARATORS (CS)

Cycle-by-Cycle Peak

Current-Limit Threshold

V

CS-PEAK

375

393

410

mV

Cycle-by-Cycle Reverse

Current-Limit Threshold

V

CS-REV

Turns AUXDRV off for the remaining

cycle if reverse current limit is exceeded

-118

-100

-88

mV

Current-Sense Blanking Time

for Reverse Current Limit

t

CS-BLANK-

REV

From AUXDRV falling edge

115

ns

Number of Consecutive Peak

Current-Limit Events to Hiccup

N

HICCUP

8

Events

Current-Sense Leading-Edge

Blanking Time

t

CS-BLANK

From NDRV rising edge

115

ns

Propagation Delay from

Comparator Input to NDRV

t

PDCS

From CS rising (10mV overdrive) to

NDRV falling (excluding leading-edge

blanking)

35

ns

Minimum On-Time

t

ON-MIN

100

150

200

ns

SLOPE COMPENSATION (CSSC)

Slope Compensation Current

Ramp Height

Current ramp’s peak added to CSSC

input per switching cycle

47

52

58

F

A

PWM COMPARATOR

Comparator Offset Voltage

V

PWM-OS

V

COMP

- V

CSSC

1.35

1.7

2

V

Current-Sense Gain

A

CS-PWM

D

V

COMP

/DV

CSSC

(Note 4)

3.1

3.33

3.6

V/V

Current-Sense Leading-Edge

Blanking Time

t

CSSC-BLANK

From NDRV rising edge

115

ns

Comparator Propagation Delay

t

PWM

Change in V

CSSC

= 10mV (including

internal leading-edge blanking)

150

ns