Table 3. parallel clock frequency range select, Table 4. modulation rate function table – Rainbow Electronics MAX9217 User Manual

Page 12

MAX9217

27-Bit, 3MHz-to-35MHz

DC-Balanced LVDS Serializer

12

______________________________________________________________________________________

Phase-Modulation Setting MOD[1:0]

The serial output edges can be phase shifted (modulated)

to reduce EMI. Table 4 shows the available settings for

phase modulation. Two shift amplitudes are available. The

parallel clock frequency should be 10MHz or higher for

the highest amplitude (MOD1 = 1, MOD0 = 0).

Termination

The MAX9217 has an integrated 100

Ω output-termina-

tion resistor. This resistor damps reflections from

induced noise and mismatches between the transmis-

sion line impedance and termination resistors at the

deserializer input. With PWRDWN = low or with the sup-

ply off, the output termination is switched out and the

LVDS output is high impedance.

Common-Mode Filter

The integrated 100

Ω output termination is made up of

two 50

Ω resistors in series. The junction of the resistors

is connected to the CMF pin for connecting an optional

common-mode filter capacitor. Connect the filter

capacitor to ground close to the MAX9217 as shown in

Figure 13. The capacitor shunts common-mode switch-

ing current to ground to reduce EMI.

RNG0

RNG1

PARALLEL

CLOCK (MHz)

SERIAL DATA RATE

(Mbps)

0

0

3 to 5

60 to 100

0

1

5 to10

100 to 200

1

0

10 to 20

200 to 400

1

1

20 to 35

400 to 700

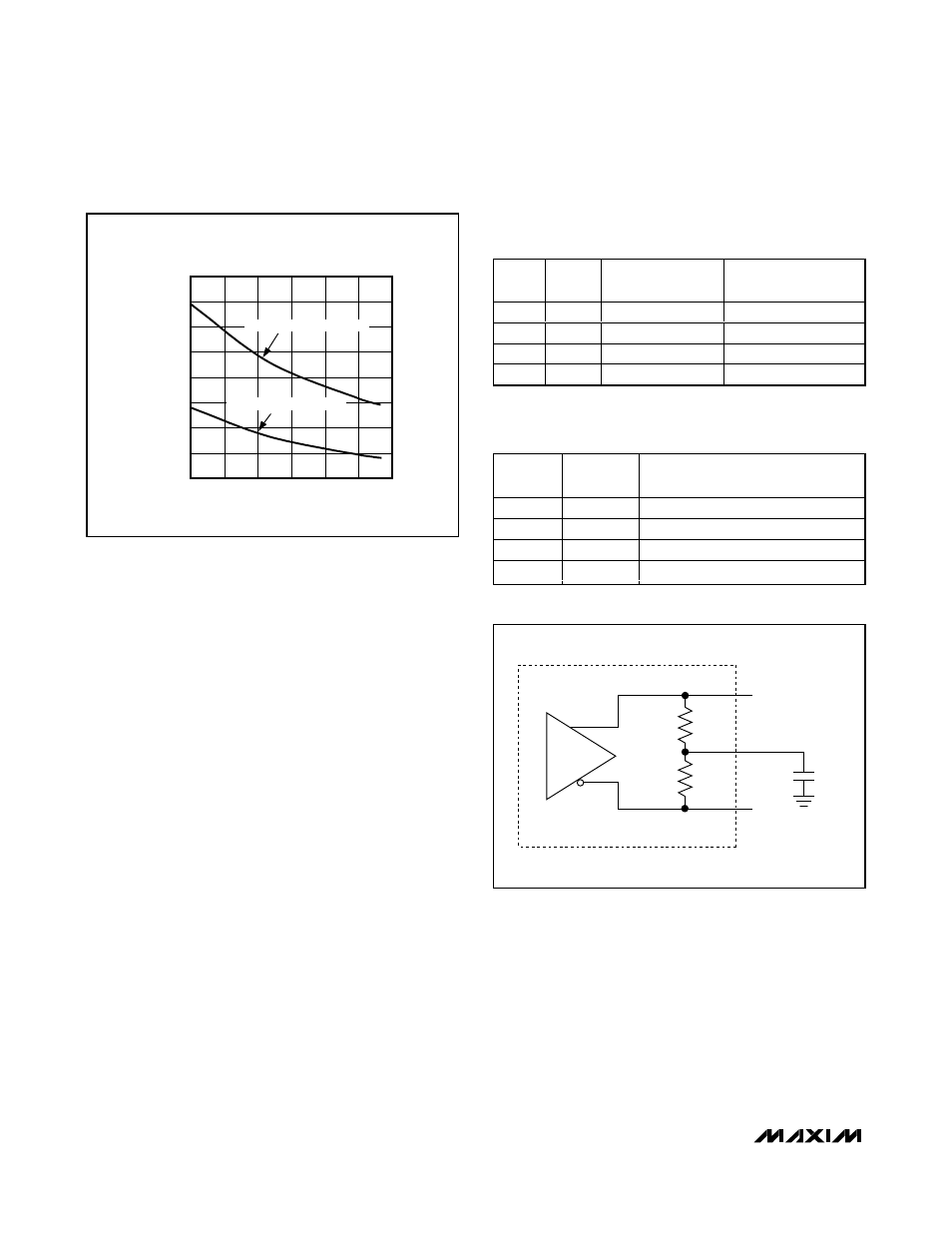

AC-COUPLING CAPACITOR VALUE

vs. PARALLEL CLOCK FREQUENCY

MAX9217 fig12

PARALLEL CLOCK FREQUENCY (MHz)

CAPACITOR VALUE (nF)

33

30

21

24

27

35

50

65

80

95

110

125

140

20

18

36

TWO CAPACITORS PER LINK

FOUR CAPACITORS PER LINK

Figure 12. AC-Coupling Capacitor Values vs. Clock Frequency

of 18MHz to 35MHz

Table 3. Parallel Clock Frequency Range

Select

MOD1

MOD0

SIMULATED PEAK POWER

REDUCTION (dB)

0

0

0 (off)

0

1

2.5

1

0

4.5

1

1

(reserved)

Table 4. Modulation Rate Function Table

OUT+

R

O

/ 2

R

O

/ 2

CMF

OUT-

C

CMF

Figure 13. Common-Mode Filter Capacitor Connection