Timing characteristics—dv, 7v to +5.25v – Rainbow Electronics MAX5735 User Manual

Page 10

MAX5732–MAX5735

32-Channel, 16-Bit, Voltage-Output

DACs with Serial Interface

10

______________________________________________________________________________________

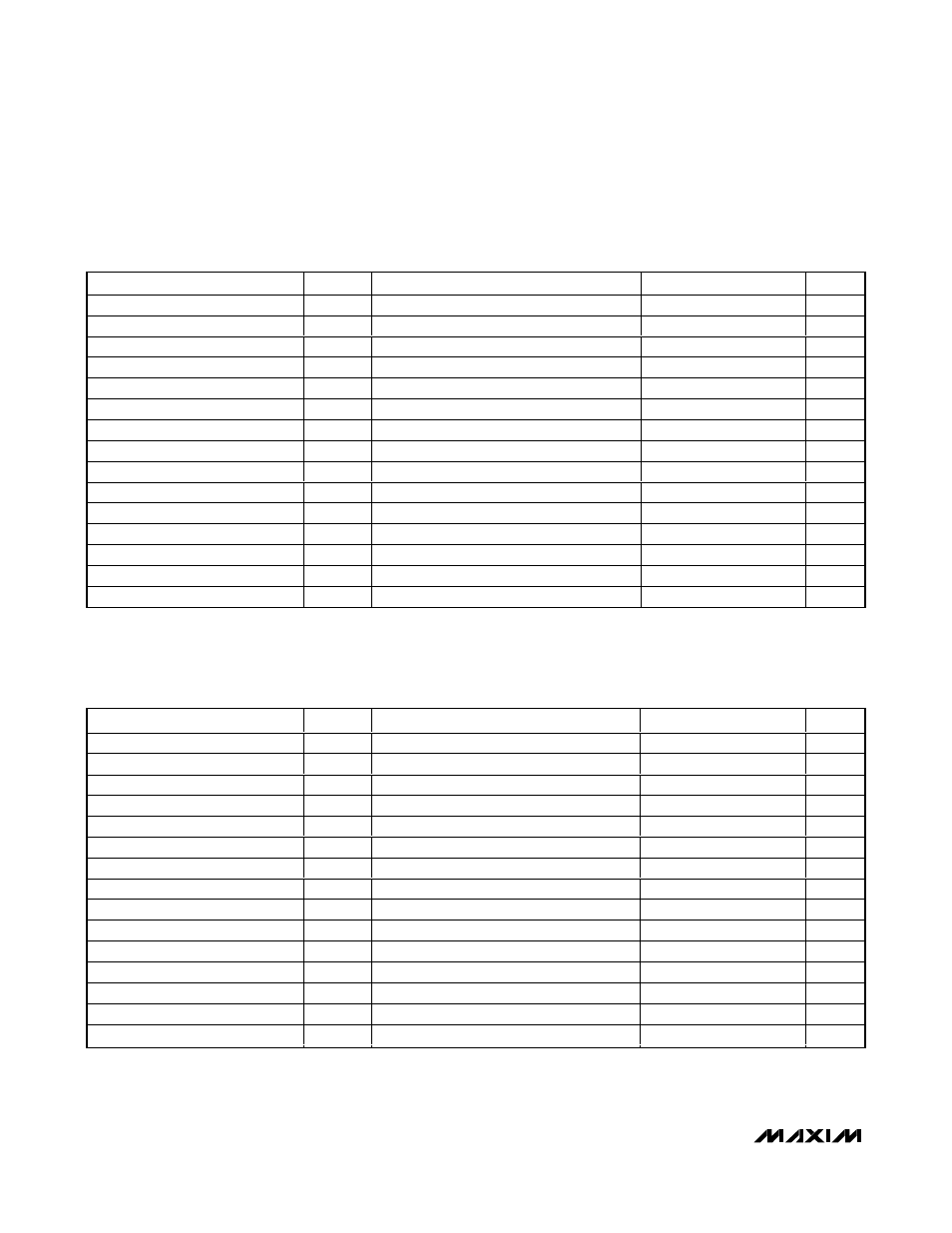

TIMING CHARACTERISTICS—DV

DD

= +2.7V to +5.25V

(Figures 2 and 3, AV

DD

= +4.75V to +5.25V, DV

DD

= +2.7V to +5.25V, AGND = DGND = REFGND = GS = 0, T

A

= T

MIN

to T

MAX

,

unless otherwise noted. Typical values are at T

A

= +25°C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Serial Clock Frequency

f

SCLK

0

25

MHz

SCLK Pulse-Width High

t

CH

10

ns

SCLK Pulse-Width Low

t

CL

10

ns

SCLK Fall to

CS Fall Setup Time

t

SCS

10

ns

CS Fall to SCLK Fall Setup Time

t

CSS

10

ns

CS Rise to SCLK Fall

t

CS1

At end of cycle in SPI mode only

18

ns

SCLK Fall to

CS Rise Setup Time

t

CS2

0

ns

DIN to SCLK Fall Setup Time

t

DS

10

ns

DIN to SCLK Fall Hold Time

t

DH

2

ns

SCLK Fall to DOUT Fall

t

SCL

Load capacitance = 20pF

25

ns

SCLK Fall to DOUT Rise

t

SDH

Load capacitance = 20pF

25

ns

CS Pulse-Width High

t

CSPWH

50

ns

CS Pulse-Width Low

t

CSPWL

20

ns

LDAC Pulse-Width Low

t

LDAC

20

ns

CLR Pulse-Width Low

t

CLR

20

ns

TIMING CHARACTERISTICS—DV

DD

= +4.75V to +5.25V

(Figures 2 and 3, AV

DD

= +4.75V to +5.25V, DV

DD

= +4.75V to +5.25V, AGND = DGND = REFGND = GS = 0, T

A

= T

MIN

to T

MAX

,

unless otherwise noted. Typical values are at T

A

= +25°C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Serial Clock Frequency

f

SCLK

0

33

MHz

SCLK Pulse-Width High

t

CH

10

ns

SCLK Pulse-Width Low

t

CL

10

ns

SCLK Fall to

CS Fall Setup Time

t

SCS

6

ns

CS Fall to SCLK Fall Setup Time

t

CSS

5

ns

CS Rise to SCLK Fall

t

CS1

At end of cycle in SPI mode only

15

ns

SCLK Fall to

CS Rise Setup Time

t

CS2

0

ns

DIN to SCLK Fall Setup Time

t

DS

10

ns

DIN to SCLK Fall Hold Time

t

DH

2

ns

SCLK Fall to DOUT Fall

t

SCL

Load capacitance = 20pF

20

ns

SCLK Fall to DOUT Rise

t

SDH

Load capacitance = 20pF

20

ns

CS Pulse-Width High

t

CSPWH

50

ns

CS Pulse-Width Low

t

CSPWL

20

ns

LDAC Pulse-Width Low

t

LDAC

20

ns

CLR Pulse-Width Low

t

CLR

20

ns