Applications information, Chip information, Digital feedthrough suppression – Rainbow Electronics MAX5842 User Manual

Page 11: Digital inputs and interface logic, Power-supply bypassing and ground management

MAX5842

Quad, 12-Bit, Low-Power, 2-Wire, Serial

Voltage-Output DAC

______________________________________________________________________________________

11

to the selected power-down mode based on the states

of PD0 and PD1 (Table 1). Any combination of the four

DACs can be controlled with a single write sequence.

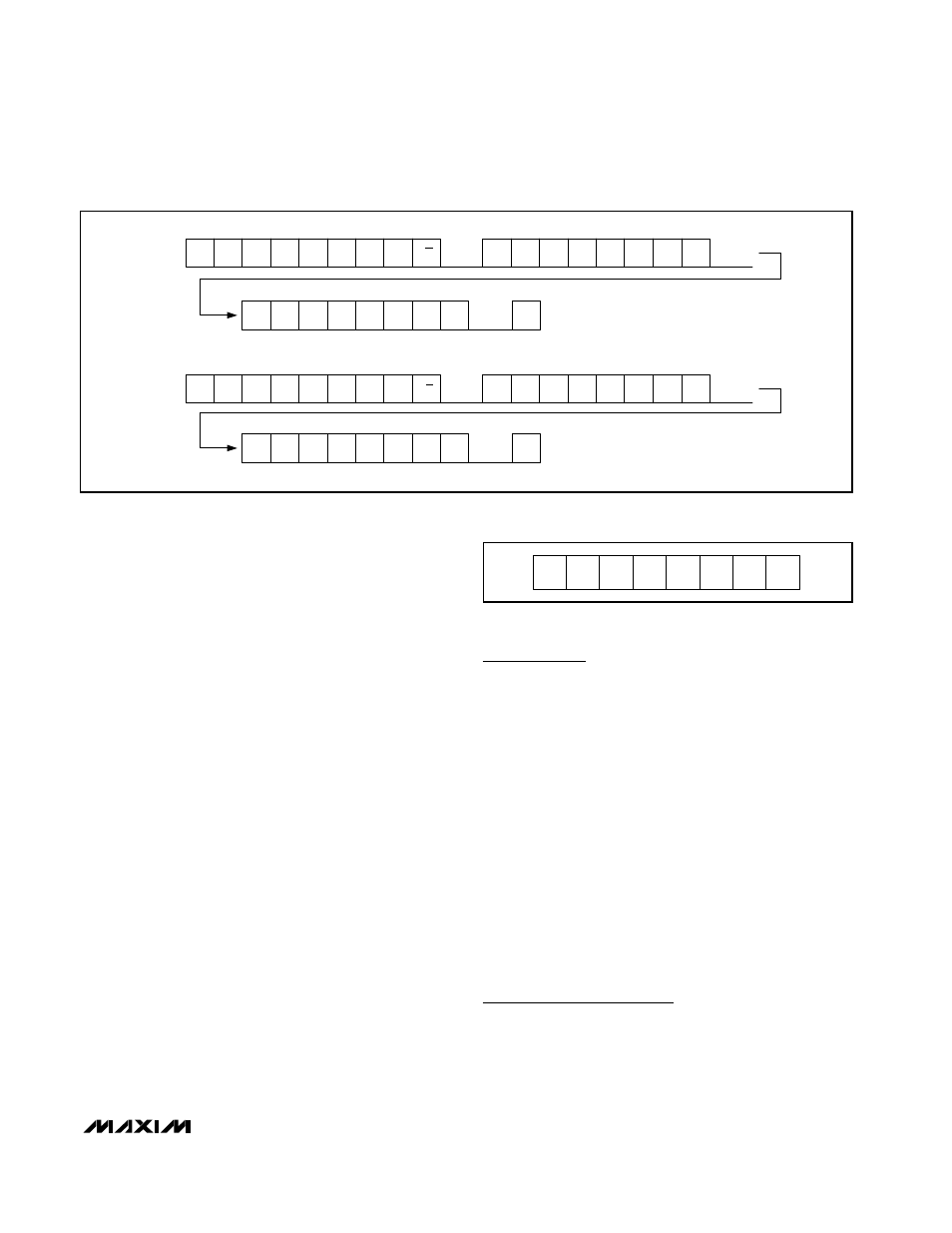

Read Data Format

In read mode (R/W = 1), the MAX5842 writes the con-

tents of the DAC register to the bus. The direction of

data flow reverses following the address acknowledge

by the MAX5842. The device transmits the first byte of

data, waits for the master to acknowledge, then trans-

mits the second byte. Figure 8 shows an example read

data sequence.

I

2

C Compatibility

The MAX5842 is compatible with existing I

2

C systems.

SCL and SDA are high-impedance inputs; SDA has an

open drain that pulls the data line low during the ninth

clock pulse. The Typical Operating Circuit shows a typ-

ical I

2

C application. The communication protocol sup-

ports the standard I

2

C 8-bit communications. The

general call address is ignored. The MAX5842 address

is compatible with the 7-bit I

2

C addressing protocol

only. No 10-bit address formats are supported.

Digital Feedthrough Suppression

When the MAX5842 detects an address mismatch, the

serial interface disconnects the SCL signal from the

core circuitry. This minimizes digital feedthrough

caused by the SCL signal on a static output. The serial

interface reconnects the SCL signal once a valid

START condition is detected.

Applications Information

Digital Inputs and Interface Logic

The MAX5842 2-wire digital interface is I

2

C/SMBus

compatible. The two digital inputs (SCL and SDA) load

the digital input serially into the DAC. Schmitt-trigger

buffered inputs allow slow-transition interfaces such as

optocouplers to interface directly to the device. The

digital inputs are compatible with CMOS logic levels.

Power-Supply Bypassing and

Ground Management

Careful PC board layout is important for optimal system

performance. Keep analog and digital signals separate

to reduce noise injection and digital feedthrough. Use a

ground plane to ensure that the ground return from

GND to the power-supply ground is short and low

impedance. Bypass V

DD

with a 0.1µF capacitor to

ground as close to the device as possible.

Chip Information

TRANSISTOR COUNT: 17,213

PROCESS: BiCMOS

S

MSB

MSB

A6

A5

A4

A3

A2

A1

A0

C3

C2

C1

C0

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

P

R/W

ACK

ACK

ACK

LSB

MSB

LSB

EXAMPLE WRITE DATA SEQUENCE

EXAMPLE WRITE TO POWER-DOWN REGISTER SEQUENCE

LSB

S

MSB

MSB

A6

A5

A4

A3

A2

A1

A0

C3

C2

C1

C0

D11

D10

D9

D8

X

X

D

C

B

A

PD1

PD0

P

R/W

ACK

ACK

ACK

LSB

MSB

LSB

LSB

Figure 6. Example Write Command Sequences

X

X

D

C

B

A

PD1

PD0

Figure 7. Extended Command Byte Definition