C-compatible interface, Electrical characteristics (continued), Timing characteristics – Rainbow Electronics MAX6651 User Manual

Page 3

MAX6650/MAX6651

Fan-Speed Regulators and Monitors

with SMBus/I

2

C-Compatible Interface

_______________________________________________________________________________________

3

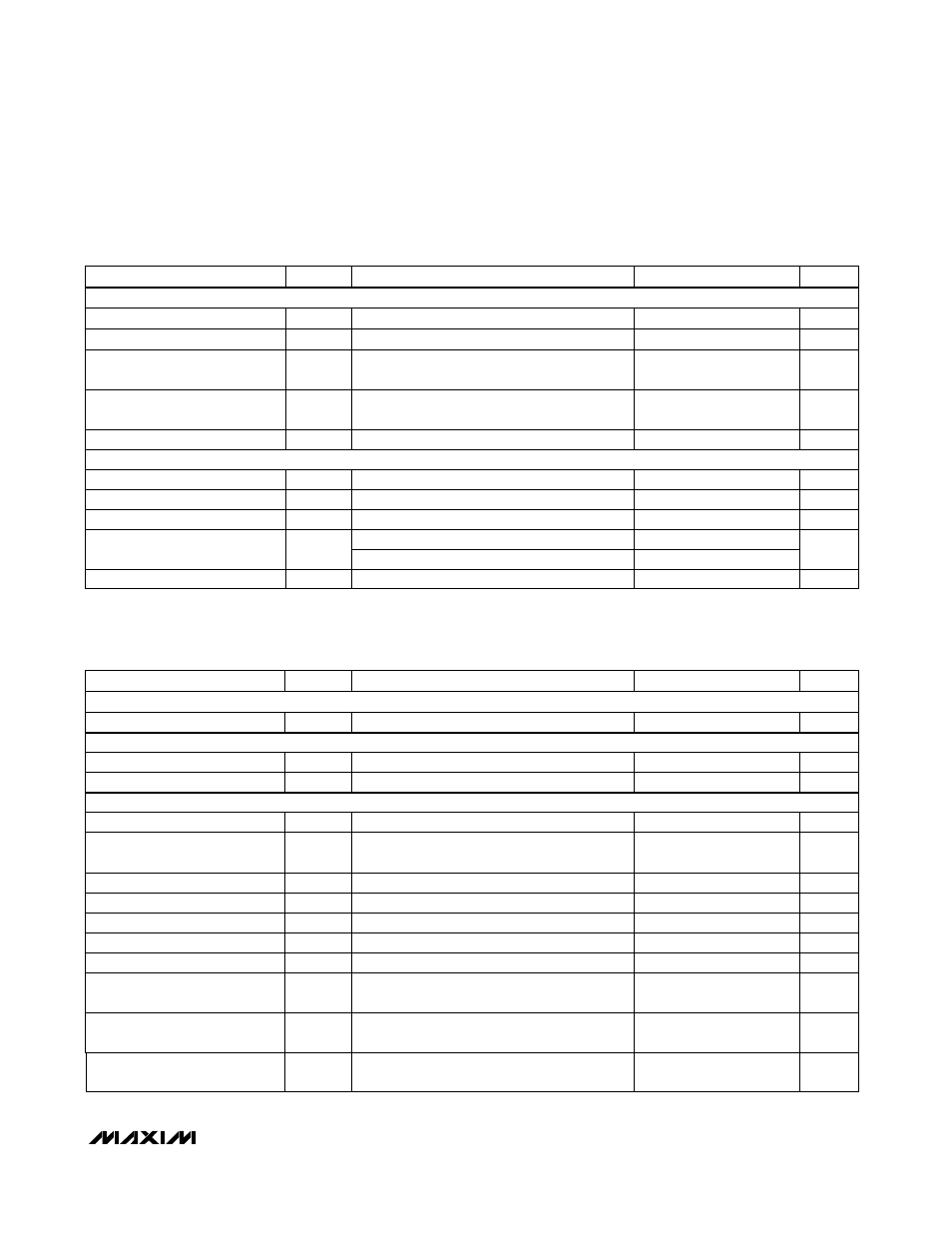

ELECTRICAL CHARACTERISTICS (continued)

(V

CC

= +3.0V to +5.5V, T

A

= -40°C to +85°C, unless otherwise noted. Typical values are at T

A

= +25°C and V

CC

= +5V.)

TIMING CHARACTERISTICS

(V

CC

= +3.0V to +5.5V, T

A

= -40°C to +85°C, unless otherwise noted. Typical values are at T

A

= +25°C and V

CC

= +5V.)

Selects slave address 1001 011 (Table 1)

Selects slave address 1001 000 (Table 1)

Selects slave address 0011 111 (Table 1)

Minimum resistance to GND, selects slave

address 0011 011 (Table 1)

V

ADD

= 0.5V

CONDITIONS

V

V

CC

- 0.05V

V

IH(ADD)

ADD Input High Voltage

V

0.1

V

IL(ADD)

ADD Input Low Voltage

I

2

C/SMBus INTERFACE (SDA, SCL)

k

Ω

9.5

10.5

R

ADD

ADD External Pulldown Resistor

to GND

k

Ω

5

R

OPEN

Open Resistance

µA

40

80

I

ADD

ADD Pullup Current

UNITS

MIN

TYP

MAX

SYMBOL

PARAMETER

V

SDA

= 0.6V

mA

6

I

SDA

Data Output Sink Current

V

CC

≤ 3.6V

V

2

V

0.8

V

IL

Input Low Voltage

0 < V

IN

< V

CC

µA

±1

Input Leakage Current

V

CC

> 3.6V

3

V

IH

Input High Voltage

mV

200

V

HYS

Input Hysteresis

ADDRESS SELECT (ADD)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

µs

500

Minimum pulse duration

Glitch Rejection

kHz

254

f

CLK

Clock Frequency

kHz

0

400

f

SCL

SCL Clock Frequency

µs

1.3

t

BUF

Bus Free Time Between Stop

and Start Condition

Hold-Time Start Condition

t

HD:STA

0.6

µs

µs

1.3

t

LOW

Low Period of the SCL Clock

High Period of the SCL Clock

t

HIGH

0.6

µs

µs

0

900

(Note 3)

t

HD:DAT

Data Hold Time

Data Setup Time

t

SU:DAT

100

ns

ns

20 + 0.1C

B

(pf)

300

(Note 4)

t

R

Rise-Time SDA/SCL Signal

(Receiving)

Fall-Time SDA/SCL Signal

(Receiving)

t

F

(Note 4)

20 + 0.1C

B

(pf)

300

ns

ns

20 + 0.1C

B

(pf)

250

I

SINK

< 6mA (Note 4)

t

F

Fall-Time SDA Signal

(Transmitting)

%

-10

+10

V

CC

= 5V

f

CLK

Clock Frequency Uncertainty

TACHOMETERS

GPIO2 (Note 2)

I

2

C/SMBus INTERFACE (Figures 3, 4)