Tyan Computer MITAC S8236 User Manual

Page 72

http://www.tyan.com

72

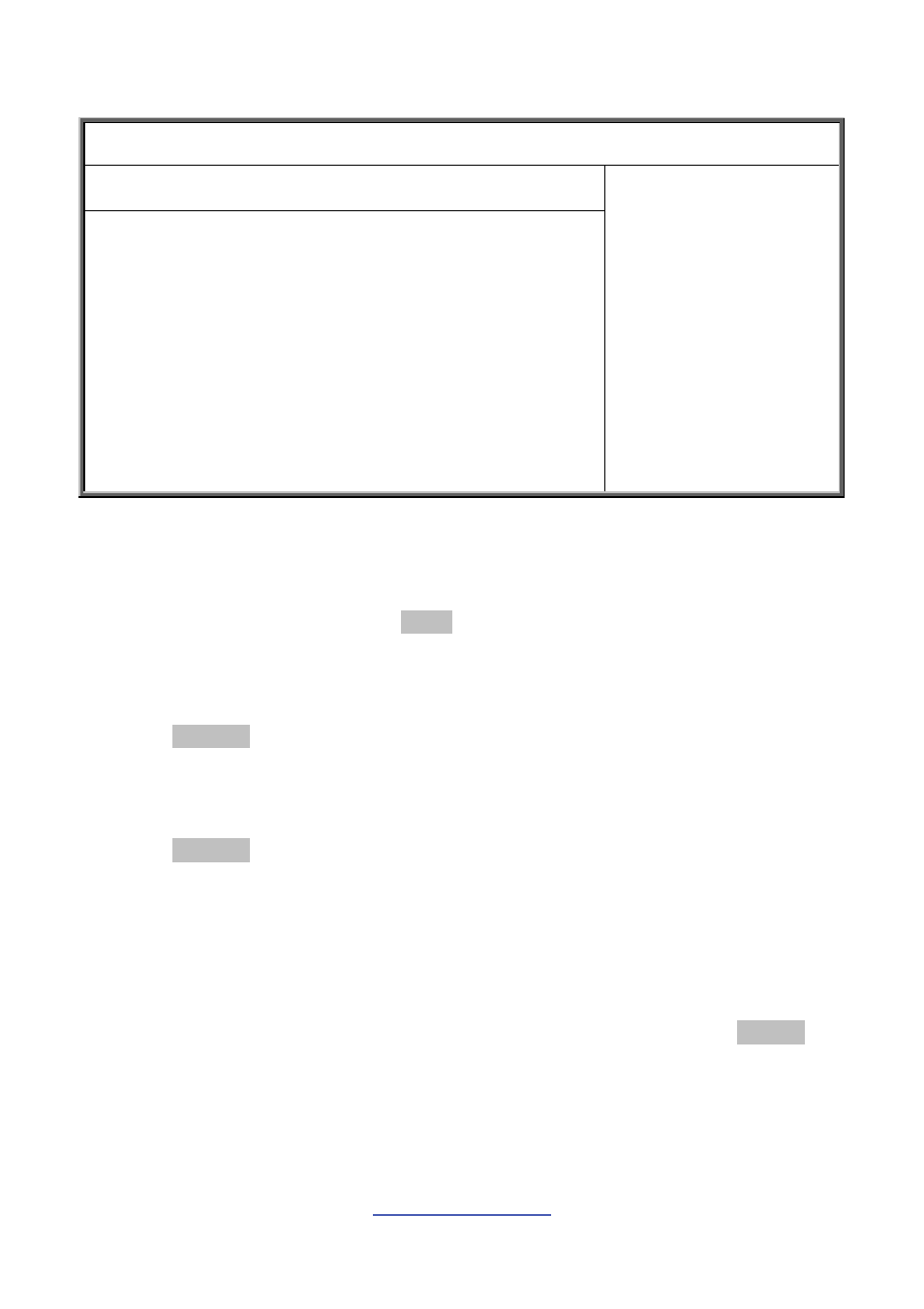

3.7.1.2 ECC Configuration

BIOS Setup Utility

Main Advanced PCI/PnP Boot Security Chipset Exit

ECC Configuration

ECC Mode

DRAM ECC Enable

DRAM SCRUB REDIRECT

DRAM BG Scrub

Data Cache BG Scrub

L2/L3 Cache BG Scrub

[Good]

[Enabled]

[Enabled]

[1.31ms]

[Disabled]

[Disabled]

Set the level of ECC

protection. Note: The

“super” ECC mode

dynamically sets the

DRAM scrub rate so all of

memory is scrubbed in 8

hours.

←

Select Screen

↑↓

Select Item

Enter Go to Sub Screen

F1 General Help

F10 Save and Exit

ESC Exit

ECC Mode

Select the level of ECC protection. Note: The “Super” ECC mode dynamically sets

the DRAM scrub rate so all of memory is scrubbed in 8 hours.

Basic / Super / Disabled / Good / Max / User

DRAM ECC Enable

DRAM ECC allows hardware to report and correct memory errors automatically

maintaining system integrity.

Enabled / Disabled

DRAM SCRUB REDIRECT

DRAM SCRUB REDIRECT allows the system to correct DRAM ECC errors

immediately when they occur, even if background scrubbing is on.

Enabled / Disabled

DRAM BG Scrub

DRAM scrubbing corrects memory errors so later reads are correct. Doing this while

memory is not being used improves performance.

Note: When AMD’s node interleave feature is enabled, BIOS will force DRAM scrub

off.

Disabled / 40ns / 80ns / 160ns / 320ns / 640ns / 1.28us / 2.56us / 5.12us /

10.2us / 20.5us / 41.0us / 81.9us / 163.8us / 327.7us / 655.4us / 1.31ms /

2.62ms / 5.24ms / 10.49ms / 20.97ms / 42.00ms / 84.00ms

Data Cache BG Scrub

Allow the L1 Data Cache RAM to be corrected while idle.