Texas Instruments 51X User Manual

Page 77

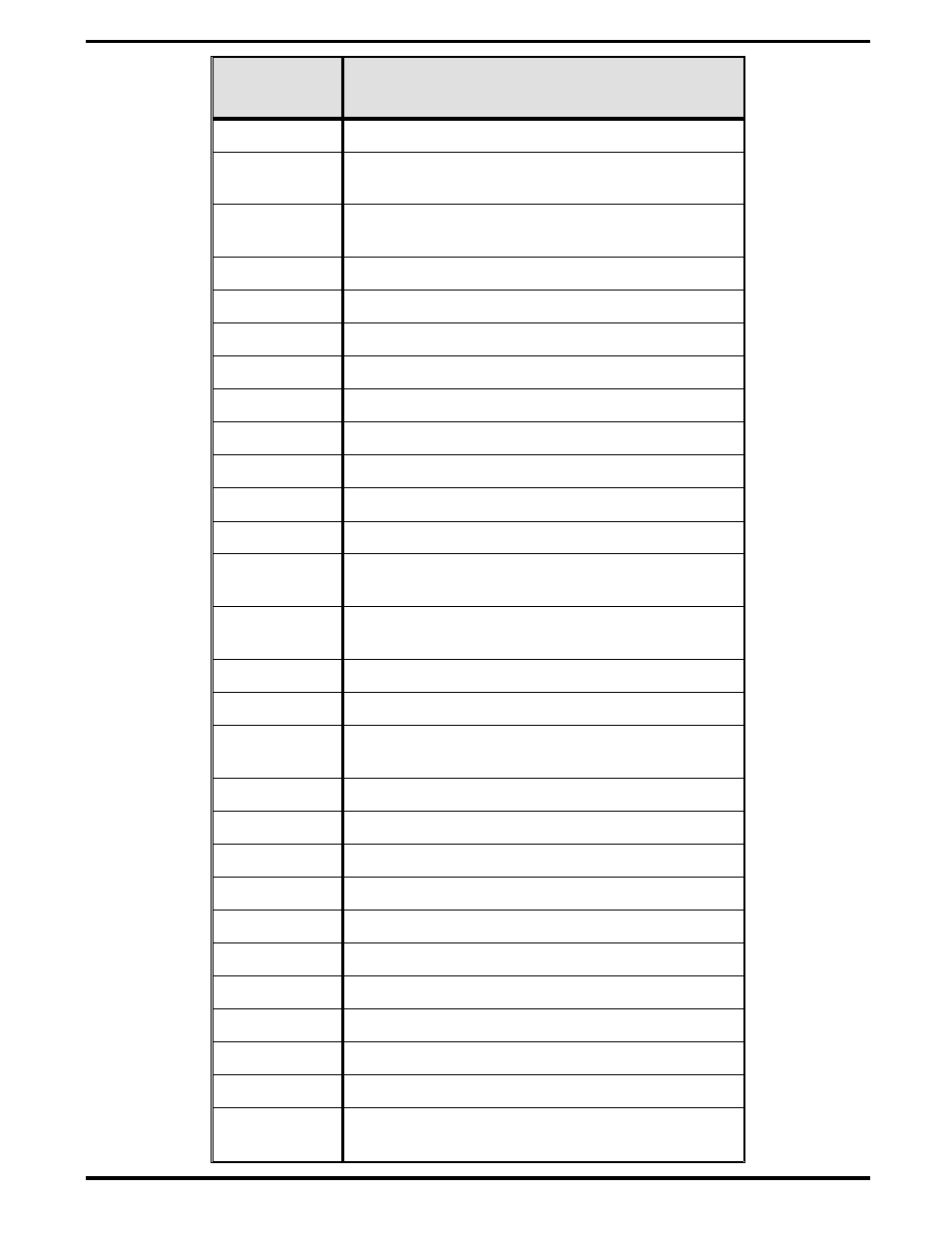

Checkpoint

No.

Description

D4h

Normal POST start

04h

Programmable Interval Timer test in-progress or

failure

06h

DMA page register write/read test in-progress or

fail

08h

RAM refresh verification in-progress or failure

09h

1st 64K RAM test in-progress

0Ah

1st 64K RAM chip or data line failure - multi-bit

0Bh

1st 64K RAM odd/even logic failure

0Ch

1st 64K RAM address line failure

0Dh

1st 64K RAM parity test in-progress or failure

10h

1st 64K RAM chip or data line failure bit 0

20h

Slave DMA register test in-progress or failure

21h

Master DMA register test in-progress or failure

22h

Master interrupt mask register test in-progress

or fail

23h

Slave interrupt mask register test in-progress or

fail

25h

Interrupt vector loading in-progress

27h

Keyboard controller test in-progress or failure

28h

CMOS power-fail and checksum checks in-

progress

29h

CMOS config info validation in-progress

2Bh

Screen memory test in-progress or failure

2Ch

Screen initialization in-progress or failure

2Dh

Screen retrace tests in-progress or failure

2Eh

Search for video ROM in-progress

30h

Screen believed operable

34h

Timer tick interrupt test in-progress or failure

35h

Shutdown test in-progress or failure

36h

Gate A20 failure

37h

Unexpected interrupt in protected mode

38h

RAM test in-progress or failure above address

0FFFFh

Error Messages A-3