Table 16, Figure 23 – Texas Instruments TMS320C642X User Manual

Page 35

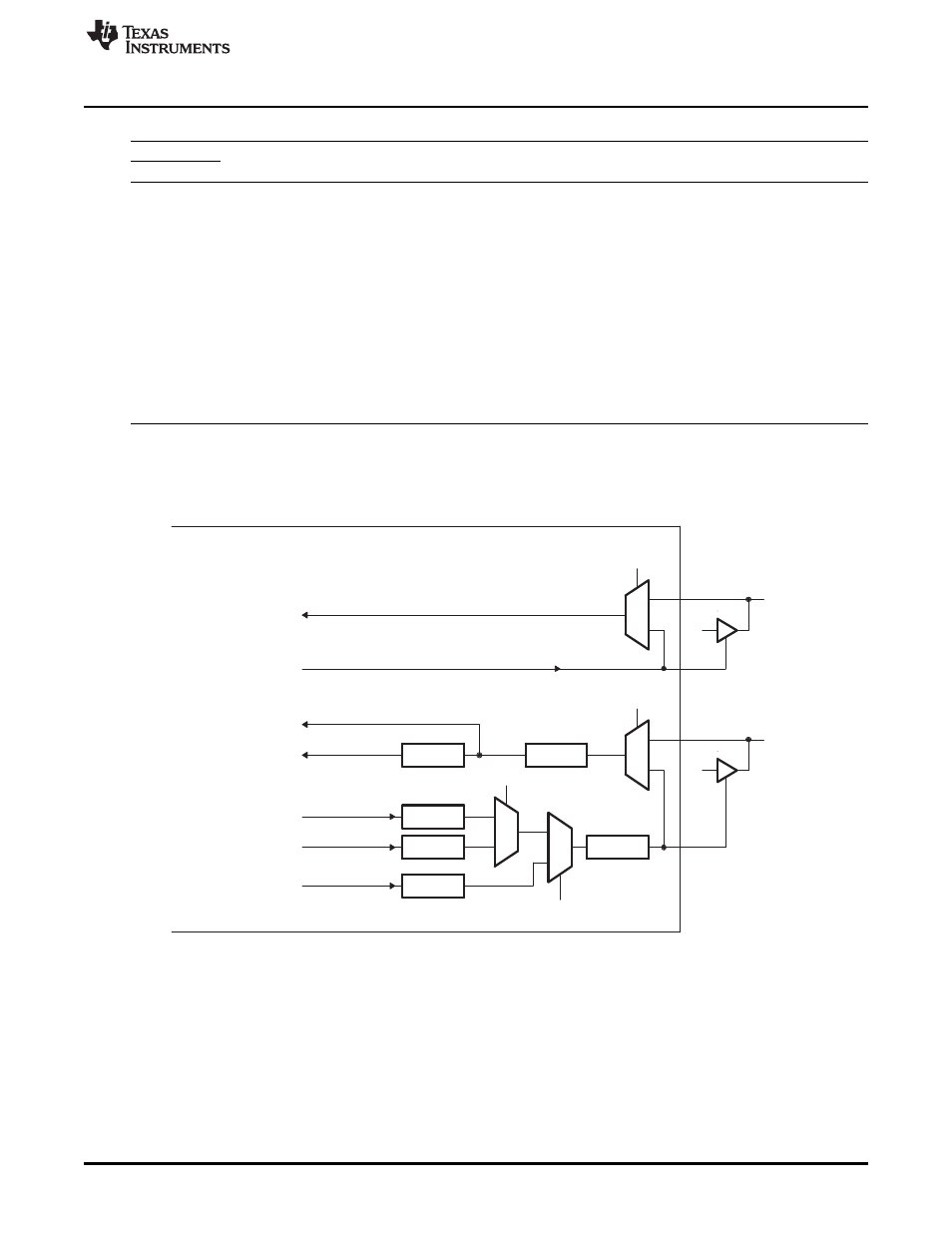

ICDRR

ICRSR

0

1

ICSAR

ICOAR

0

1

ICDXR

ICXSR

0

1

0

0

DLB

SCL_IN

SCL_OUT

Address/data

To internal I2C logic

From internal I2C logic

To internal I2C logic

To ARM CPU or EDMA

From ARM CPU or EDMA

From ARM CPU or EDMA

From ARM CPU or EDMA

SCL

SDA

I2C peripheral

DLB

DLB

www.ti.com

Registers

Table 16. How the MST and FDF Bits Affect the Role of TRX Bit

ICMDR Bit

MST

FDF

I2C State

Function of TRX Bit

0

0

In slave mode but not free data format

TRX is a don't care. Depending on the command from the master, the I2C

mode

responds as a receiver or a transmitter.

0

1

In slave mode and free data format

The free data format mode requires that the transmitter and receiver be

mode

fixed. TRX identifies the role of the I2C:

TRX = 0: The I2C is a receiver.

TRX = 1: The I2C is a transmitter.

1

0

In master mode but not free data

TRX identifies the role of the I2C:

format mode

TRX = 0: The I2C is a receiver.

TRX = 1: The I2C is a transmitter.

1

1

In master mode and free data format

The free data format mode requires that the transmitter and receiver be

mode

fixed. TRX identifies the role of the I2C:

TRX = 0: The I2C is a receiver.

TRX = 1: The I2C is a transmitter.

Figure 23. Block Diagram Showing the Effects of the Digital Loopback Mode (DLB) Bit

35

SPRUEN0D – March 2011

Inter-Integrated Circuit (I2C) Peripheral

© 2011, Texas Instruments Incorporated