2 data validity, 5 start and stop conditions – Texas Instruments TMS320C642X User Manual

Page 12

Data line

stable data

Change of data

allowed

SDA

SCL

SDA

SCL

START

condition (S)

condition (P)

STOP

Peripheral Architecture

www.ti.com

2.4.2

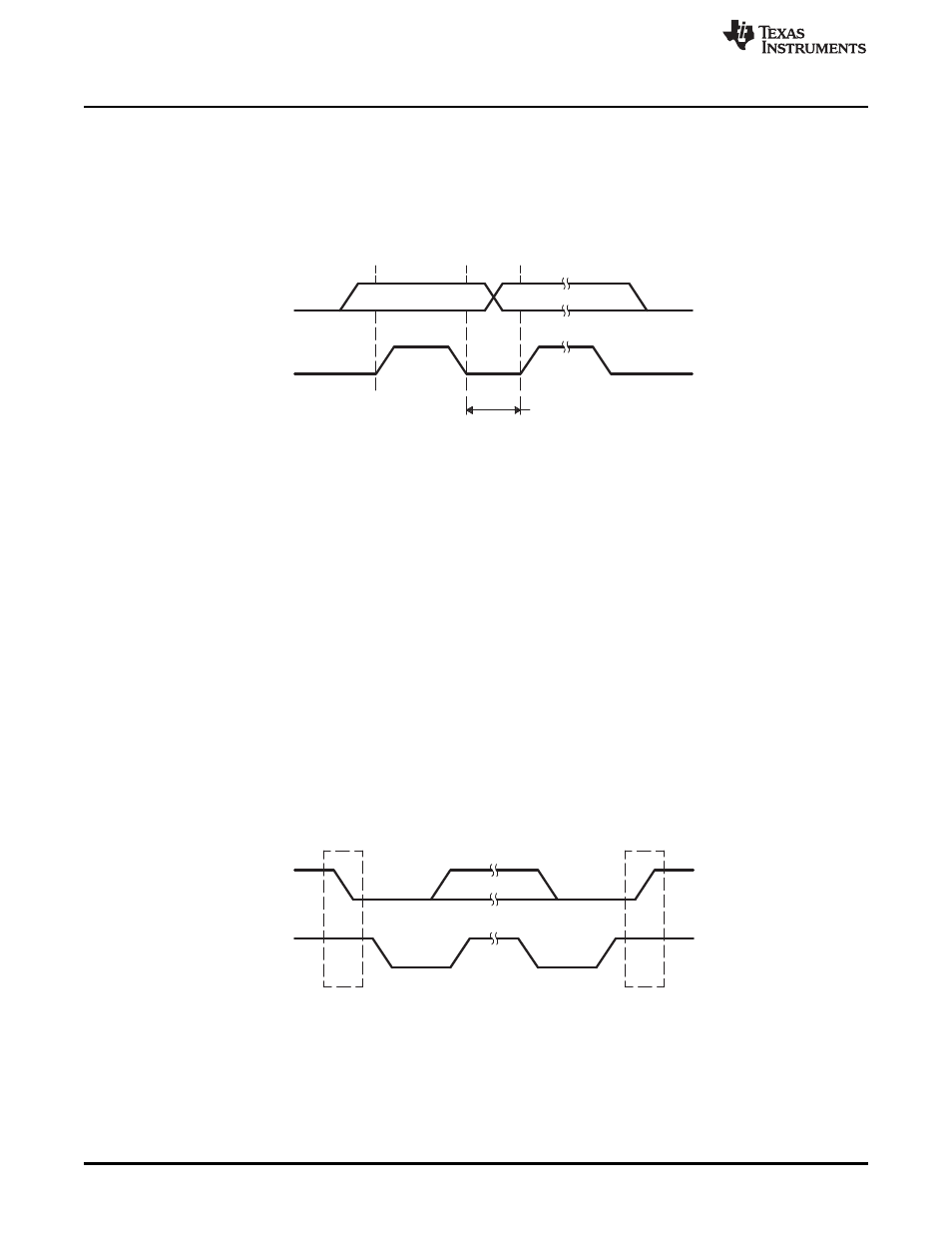

Data Validity

The data on SDA must be stable during the high period of the clock (see

). The high or low state

of the data line, SDA, can change only when the clock signal on SCL is low.

Figure 5. Bit Transfer on the I2C-Bus

2.5

START and STOP Conditions

The I2C peripheral can generate START and STOP conditions when the peripheral is configured to be a

master on the I2C-bus, as shown in

:

•

The START condition is defined as a high-to-low transition on the SDA line while SCL is high. A

master drives this condition to indicate the start of a data transfer.

•

The STOP condition is defined as a low-to-high transition on the SDA line while SCL is high. A master

drives this condition to indicate the end of a data transfer.

The I2C-bus is considered busy after a START condition and before a subsequent STOP condition. The

bus busy (BB) bit of ICSTR is 1. The bus is considered free between a STOP condition and the next

START condition. The BB is 0.

The master mode (MST) bit and the START condition (STT) bit in ICMDR must both be 1 for the I2C

peripheral to start a data transfer with a START condition. The STOP condition (STP) bit must be set to 1

for the I2C peripheral to end a data transfer with a STOP condition. A repeated START condition

generates when BB is set to 1 and STT is also set to 1. See

for a description of ICMDR

(including the MST, STT, and STP bits).

Figure 6. I2C Peripheral START and STOP Conditions

12

Inter-Integrated Circuit (I2C) Peripheral

SPRUEN0D – March 2011

© 2011, Texas Instruments Incorporated