8 i2c data transmit register (icdxr), Section 3.8 – Texas Instruments TMS320C642X User Manual

Page 31

www.ti.com

Registers

3.8

I2C Data Transmit Register (ICDXR)

The CPU or EDMA writes transmit data to the I2C data transmit register (ICDXR). The ICDXR can accept

a data value of up to 8 bits. When writing a data value with fewer than 8 bits, the written data must be

right-aligned in the D bits. The number of data bits is selected by the bit count bits (BC) of ICMDR. Once

data is written to ICDXR, the I2C copies the contents of ICDXR into the I2C transmit shift register

(ICXSR). The ICXSR shifts out the transmit data from the SDA pin. The CPU and the EDMA controller

cannot access ICXSR.

The I2C data transmit register (ICDXR) is shown in

and described in

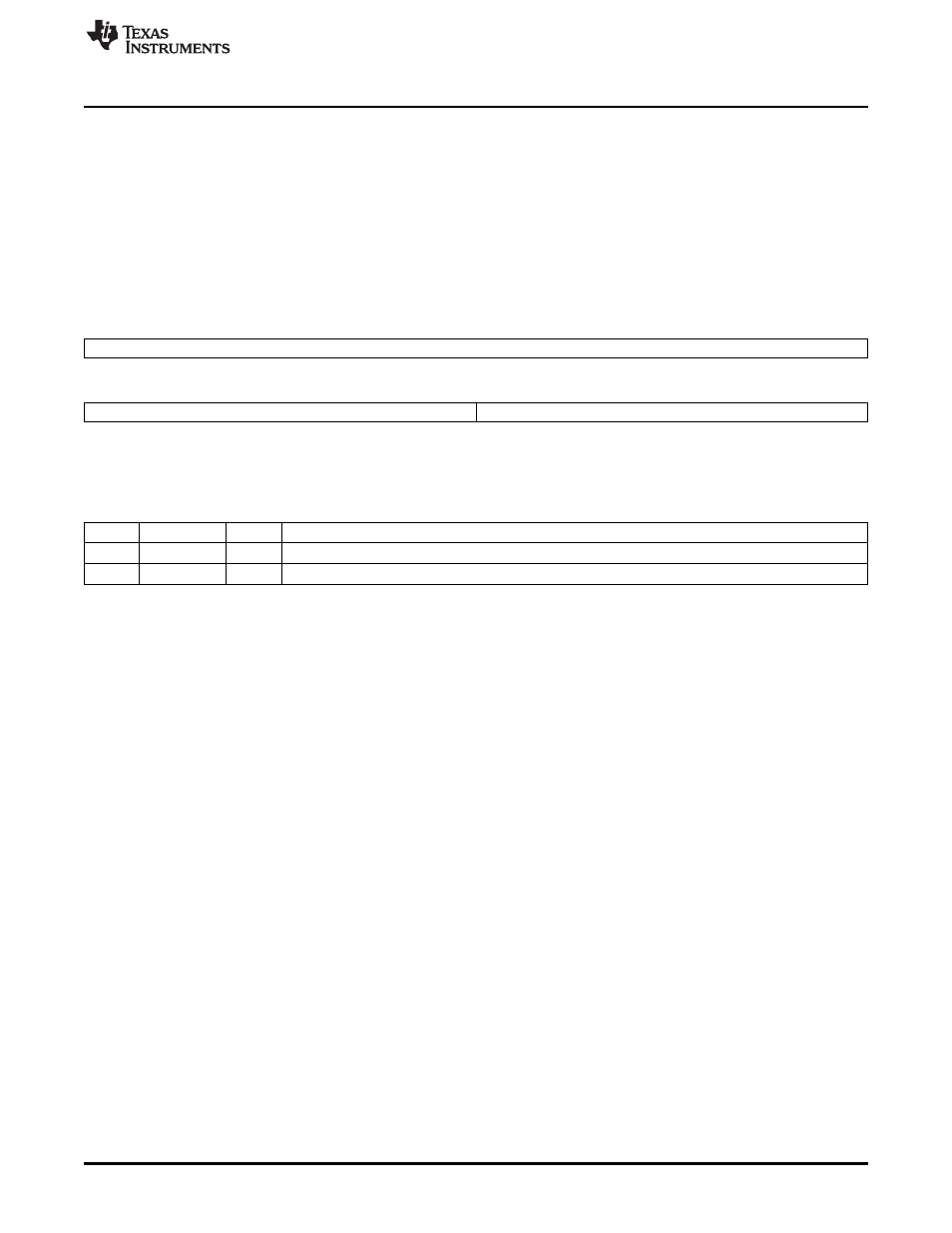

Figure 21. I2C Data Transmit Register (ICDXR)

31

16

Reserved

R-0

15

8

7

0

Reserved

D

R-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 13. I2C Data Transmit Register (ICDXR) Field Descriptions

Bit

Field

Value

Description

31-8

Reserved

0

These reserved bit locations are always read as zeros. A value written to this field has no effect.

7-0

D

0-FFh

Transmit data.

31

SPRUEN0D – March 2011

Inter-Integrated Circuit (I2C) Peripheral

© 2011, Texas Instruments Incorporated