2 i2c interrupt mask register (icimr), Section 3.2 – Texas Instruments TMS320C642X User Manual

Page 24

Registers

www.ti.com

3.2

I2C Interrupt Mask Register (ICIMR)

The I2C interrupt mask register (ICIMR) is used to individually enable or disable I2C interrupt requests.

The I2C interrupt mask register (ICIMR) is shown in

and described

.

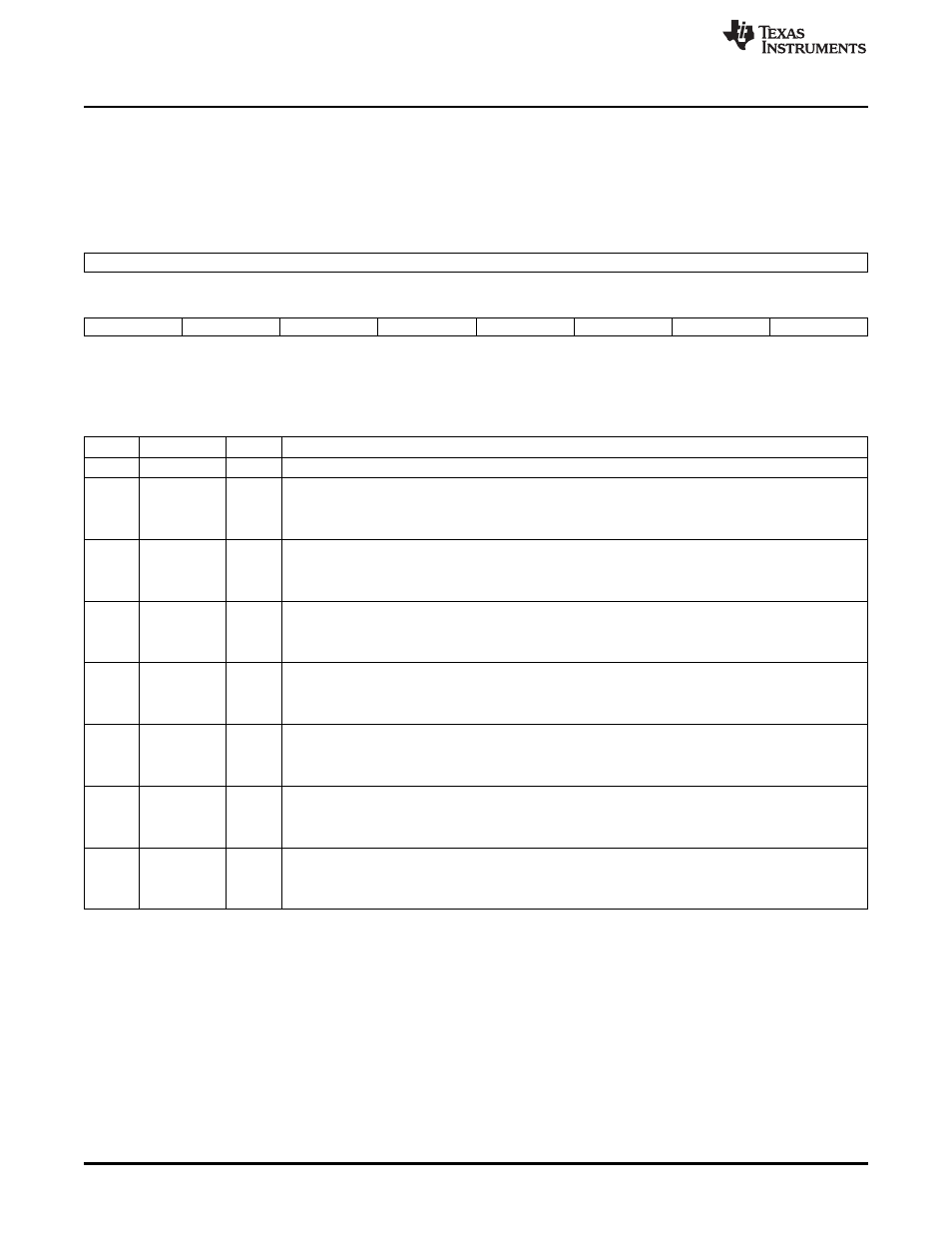

Figure 14. I2C Interrupt Mask Register (ICIMR)

31

8

Reserved

R-0

7

6

5

4

3

2

1

0

Reserved

AAS

SCD

ICXRDY

ICRRDY

ARDY

NACK

AL

R-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 6. I2C Interrupt Mask Register (ICIMR) Field Descriptions

Bit

Field

Value

Description

31-7

Reserved

0

These reserved bit locations are always read as zeros. A value written to this field has no effect.

6

AAS

Address-as-slave interrupt enable bit.

0

Interrupt request is disabled.

1

Interrupt request is enabled.

5

SCD

Stop condition detected interrupt enable bit.

0

Interrupt request is disabled.

1

Interrupt request is enabled.

4

ICXRDY

Transmit-data-ready interrupt enable bit.

0

Interrupt request is disabled.

1

Interrupt request is enabled.

3

ICRRDY

Receive-data-ready interrupt enable bit.

0

Interrupt request is disabled.

1

Interrupt request is enabled.

2

ARDY

Register-access-ready interrupt enable bit.

0

Interrupt request is disabled.

1

Interrupt request is enabled.

1

NACK

No-acknowledgment interrupt enable bit.

0

Interrupt request is disabled.

1

Interrupt request is enabled.

0

AL

Arbitration-lost interrupt enable bit

0

Interrupt request is disabled.

1

Interrupt request is enabled.

24

Inter-Integrated Circuit (I2C) Peripheral

SPRUEN0D – March 2011

© 2011, Texas Instruments Incorporated