Expanded functions – Toshiba PROSEC T3H User Manual

Page 63

User’s Manual

61

2. Expanded Functions

Note

•

Edge execution modifier is also available for this instruction.

•

The XFER instruction is not executed as error in the following cases. (ERF = S0051 is set to ON)

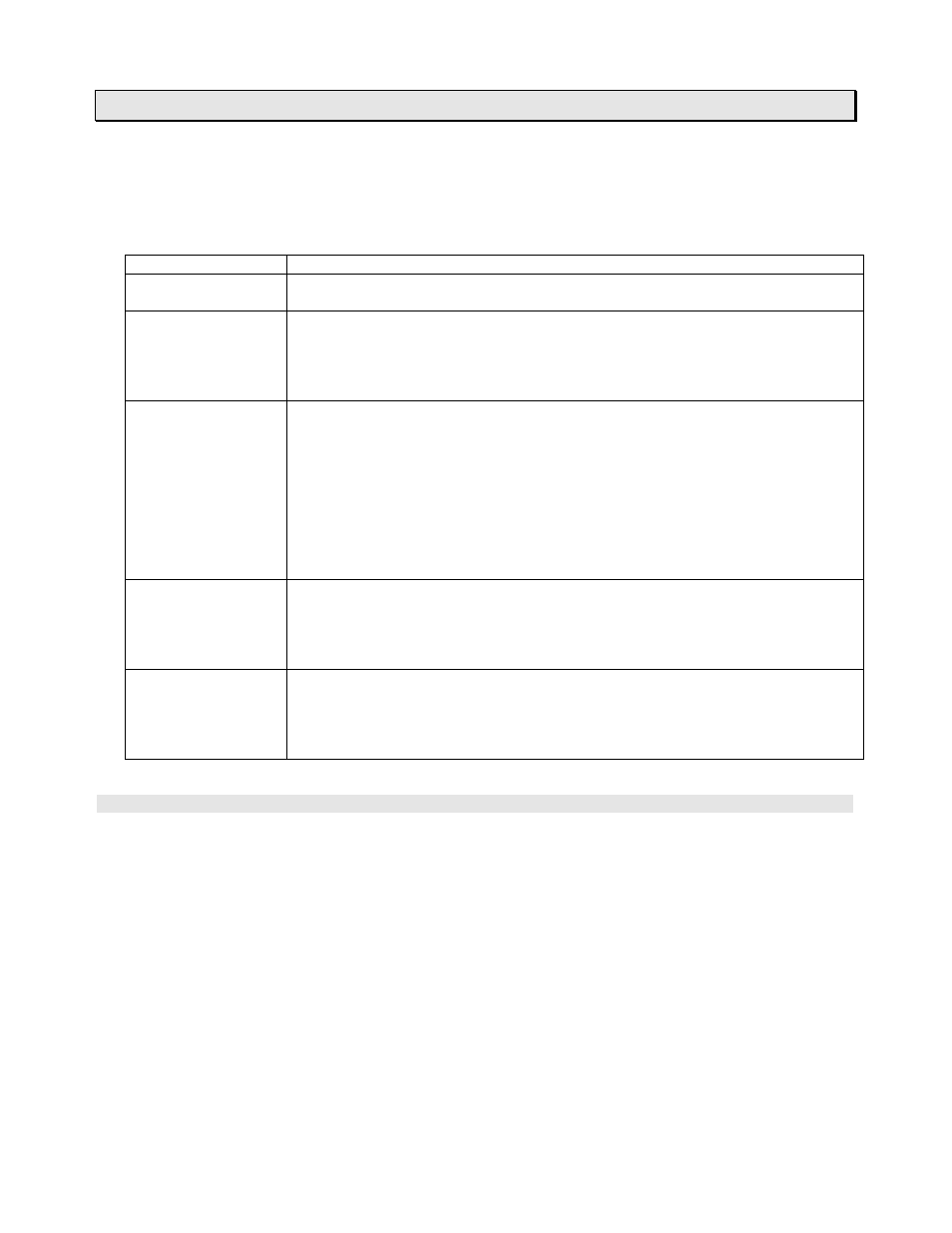

Transfer Error

cause

Between CPU

registers

1)

When the transfer size is 0 or more than 256.

2)

When the source/destination table of transfer is out of the valid range.

CPU register to

expanded F register

1)

When the transfer size is 0 or more than 256.

2)

When the source/destination table of transfer is out of the valid range.

3)

When IC memory card is not installed or MMR setting is not made.

4)

When the IC memory card is write-protect state. (for data writing)

5)

When program is stored in the IC memory card. (detected only T3H)

CPU register to

S20/S20LP

1)

When the transfer size is 0 or more than 256.

2)

When the source/destination table of transfer is out of the valid range.

3)

When channel designation is other than 1 or 2. (other than 1 for T2)

4)

When S20/S20LP is not installed or not allocated.

5)

When status flag area is not sufficient.

6)

When an odd address is designated as the leading address in the case of

S20/S20LP is set as double-word access.

7)

When the transfer size is odd address in the case of S20/S20LP is set as

double-word

access.

8)

When the S20/S20LP module is not normal.

CPU register to

EEPROM

1)

When the transfer size is 0 or more than 256.

2)

When the source/destination table of transfer is out of the valid range.

3)

When the data writing address range exceeds page boundary.

4)

When this instruction is executed during EEPROM access inhibited (10 ms).

5)

When the CPU does not have EEPROM.

Others

1)

When source/destination designation is invalid.

2)

When an invalid transfer combination is designated.

3)

When the index modification is used for an operand and register boundary

error is occurred as the result of the index modification. (in this case, the

instruction output comes OFF)