Application headers – Renesas SH7201 User Manual

Page 22

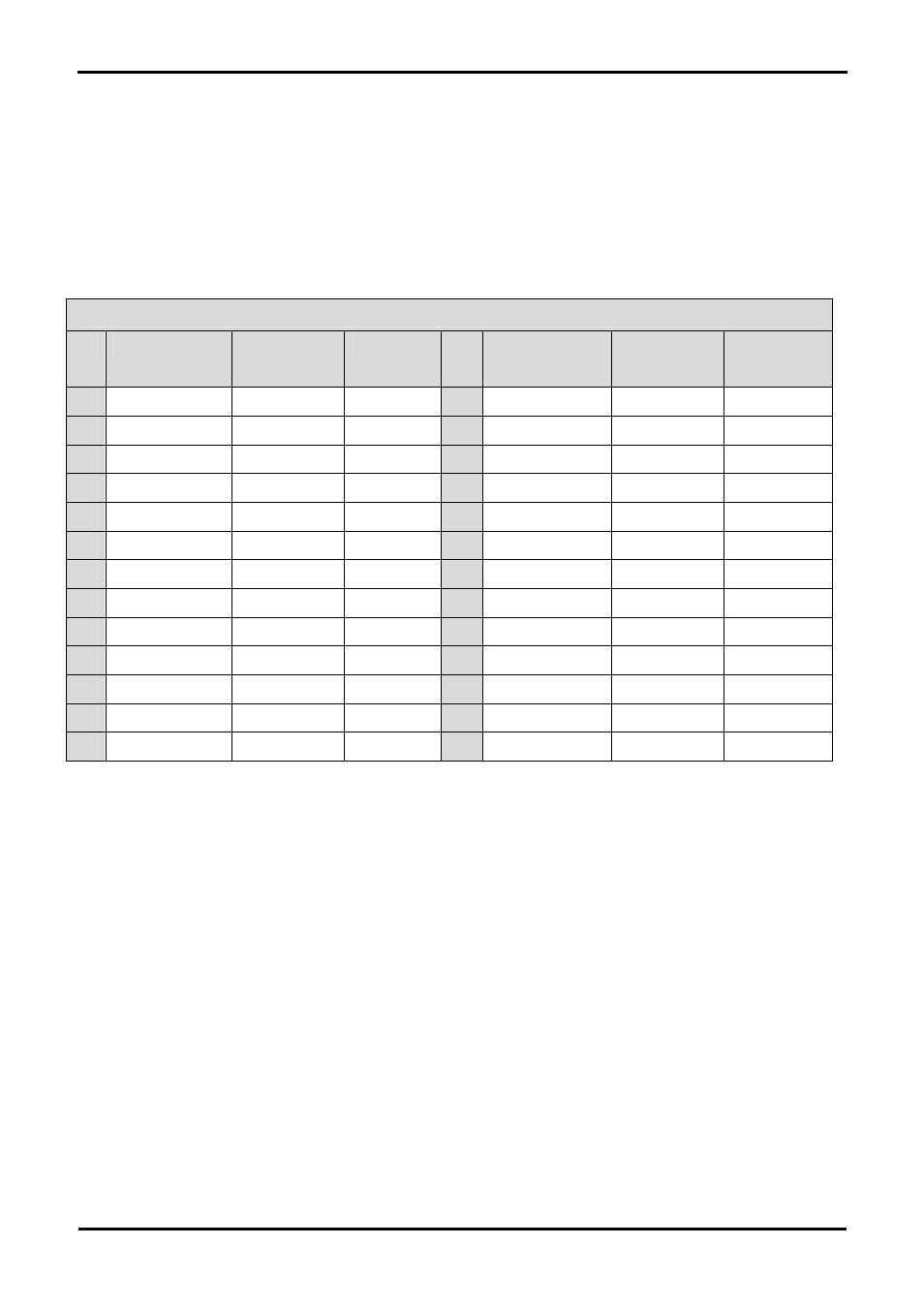

8.2.Application Headers

show the standard application header connections.

Note: Asterisk indications apply to all tables in this section

* marks pins where a the link to the microcontroller pin is via a 100R resistor and to BOARD VCC via a 4k7 resistor (100R ID & 4k7 ID)

** marks pins where a the link to the microcontroller pin is open circuit due to unfitted link (link ID in brackets)

*** marks pins where a the link to the microcontroller pin is via a fitted 0R link (link ID in brackets)

JA1

Pin

Header Name

CPU board

Signal Name

Device Pin

Pin

Header Name

CPU board

Signal Name

Device Pin

1 5V

CON_5V

-

14 DAC1

DA1

93***

(R10)

2 0V(5V)

GROUND

-

15 IO_0

IO0

95

3 3V3

CON_3V3

-

16 IO_1

IO1

96

4 0V(3V3)

GROUND

-

17 IO_2

IO2

97

5 AVcc

CON_AVCC 84**

(R57) 18 IO_3

IO3

98

6 AVss

AVSS

94

19 IO_4

IO4

99

7 AVref

CON_VREF 85**

(R39) 20 IO_5

IO5

100

8 ADTRG

ADTRGn

57**

(R59) 21 IO_6

IO6

101

9 AD0

AN0

86**

(R21) 22 IO_7

IO7

102

10 AD1

AN1

87

23 IRQ3

IRQ3n

56

11 AD2

AN2

88

24 IIC_EX

-

-

12 AD3

AN3

89

25

IIC_SDA

SDA2

106* (R13 & R4)

13 DAC0

DA0

92***

(R9) 26

IIC_SCL

SCL2

105* (R12 & R3)

Table 8-5: JA1 Standard Generic Header

18