NEC uPD78056Y User Manual

Page 529

529

CHAPTER 23 STANDBY FUNCTION

(d) Clear upon RESET input

When a RESET signal is input, the HALT mode is released, and as is the case with normal reset

operation, a program is executed after branch to the reset vector address.

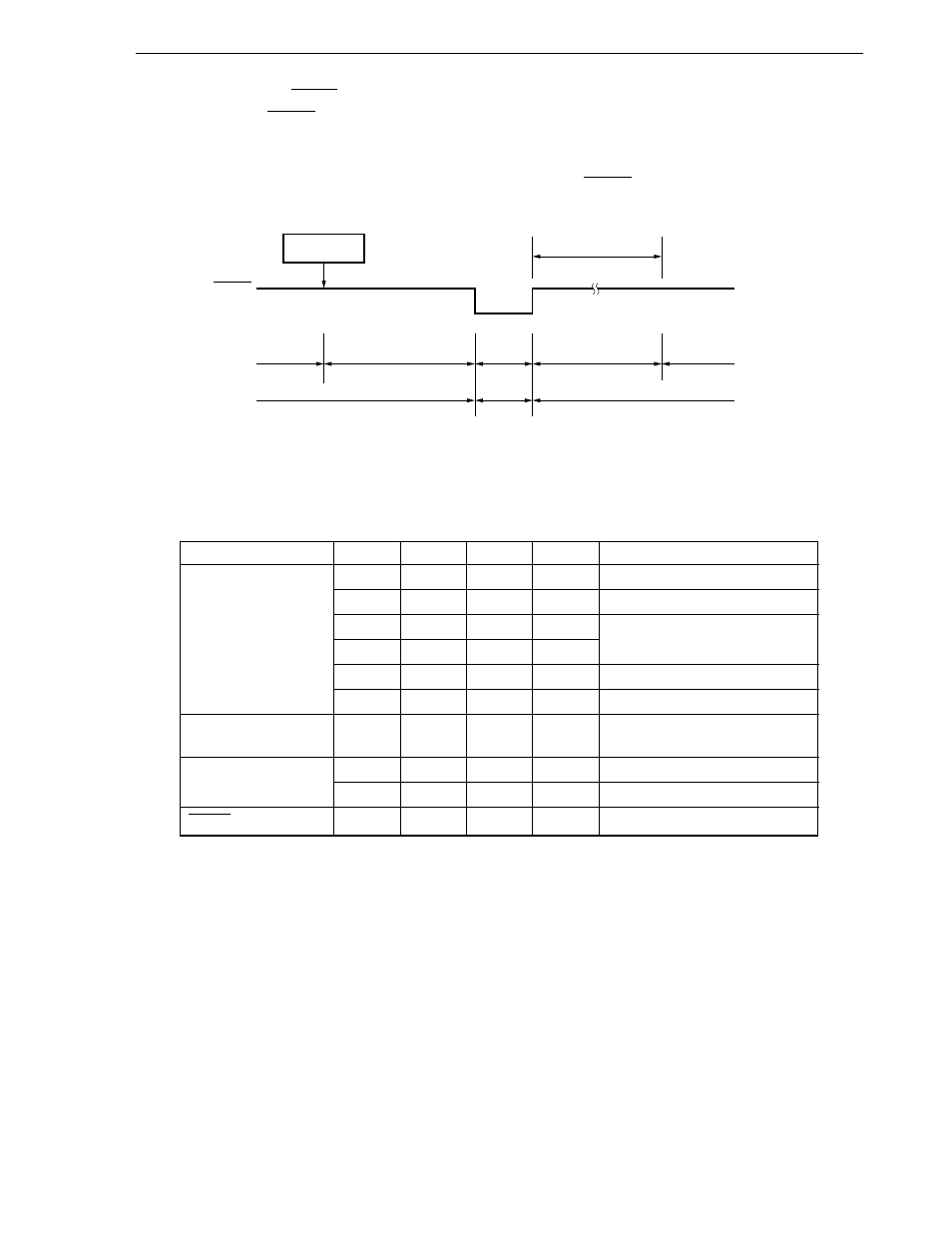

Figure 23-3. HALT Mode Release by RESET Input

Remarks 1. f

X

: main system clock oscillation frequency

2. ( ): f

X

: 5.0 MHz

Table 23-2. Operation after HALT Mode Release

Release Source

MK

××

PR

××

IE

ISP

Operation

Maskable interrupt

0

0

0

×

Next address instruction execution

request

0

0

1

×

Interrupt service execution

0

1

0

1

Next address instruction execution

0

1

×

0

0

1

1

1

Interrupt service execution

1

Ч

Ч

Ч

HALT mode hold

Non-maskable interrupt

–

–

Ч

Ч

Interrupt service execution

request

Test input

0

–

Ч

Ч

Next address instruction execution

1

–

Ч

Ч

HALT mode hold

RESET input

–

–

Ч

Ч

Reset processing

Remark x: Don't care

HALT

Instruction

RESET

Signal

Operating

Mode

Clock

Reset

Period

HALT Mode

Oscillation

Oscillation

stop

Oscillation

Stabilization

Wait Status

Operating

Mode

Oscillation

Wait

(2

17

/f

x

: 26.2 ms)