NEC uPD78056Y User Manual

Page 106

106

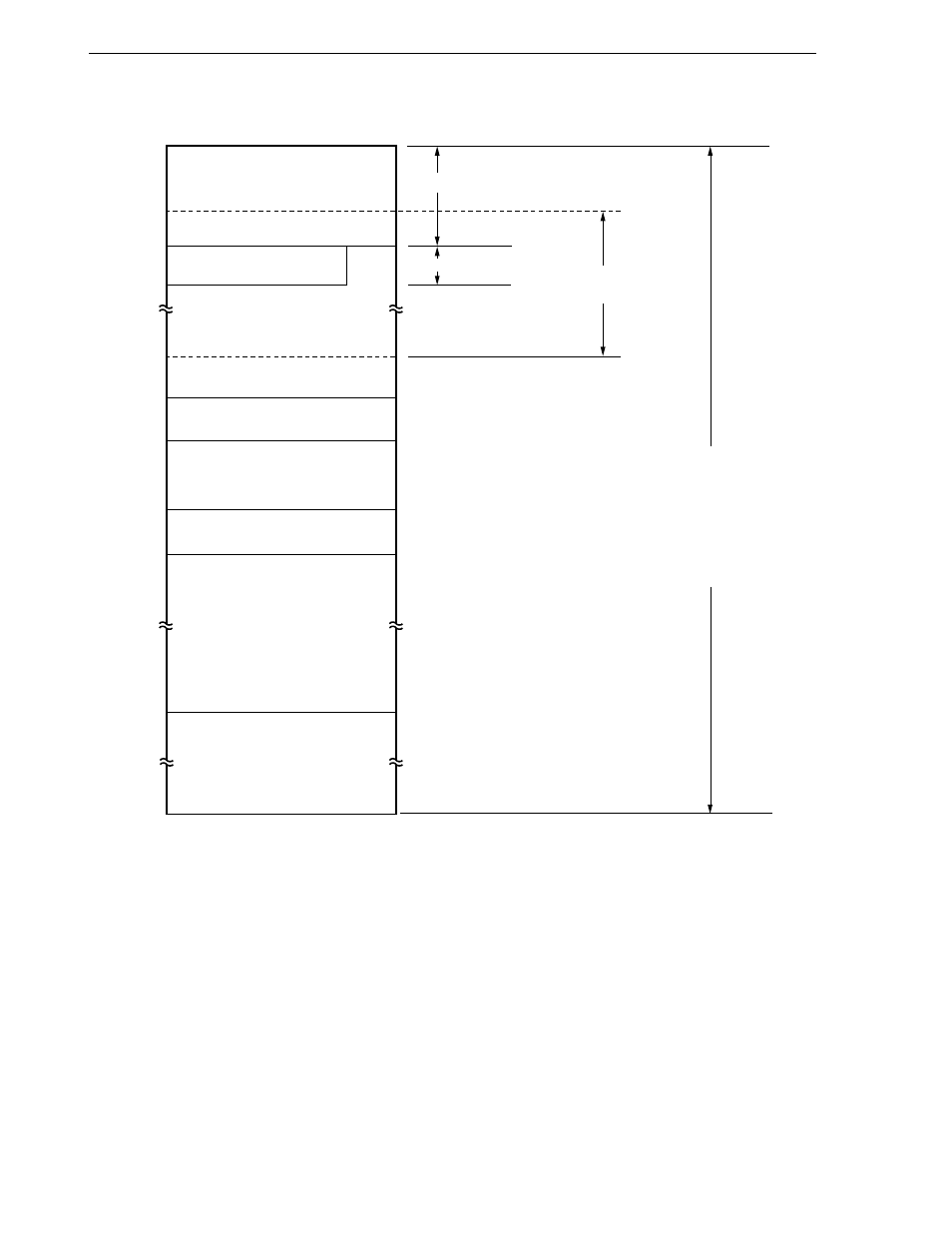

CHAPTER 5 CPU ARCHITECTURE

Figure 5-14. Data Memory Addressing (

µ

PD78056, 78056Y)

0000H

General Registers

32

×

8 bits

Internal ROM

49152

×

8 bits

Internal Buffer RAM

32

×

8 bits

External Memory

14976

×

8 bits

Reserved

C000H

BFFFH

FA80H

FA7FH

FAC0H

FABFH

FAE0H

FADFH

FEE0H

FEDFH

FF00H

FEFFH

FFFFH

Internal High-speed RAM

1024

×

8 bits

Reserved

FB00H

FAFFH

FF20H

FF1FH

FE20H

FE1FH

Special Function

Registers (SFRs)

256

×

8 bits

SFR Addressing

Register Addressing

Short Direct

Addressing

Direct Addressing

Register Indirect

Addressing

Based Addressing

Based Indexed

Addressing

This manual is related to the following products: