NEC uPD78056Y User Manual

Page 475

475

CHAPTER 19 SERIAL INTERFACE CHANNEL 2

• In case of parity error

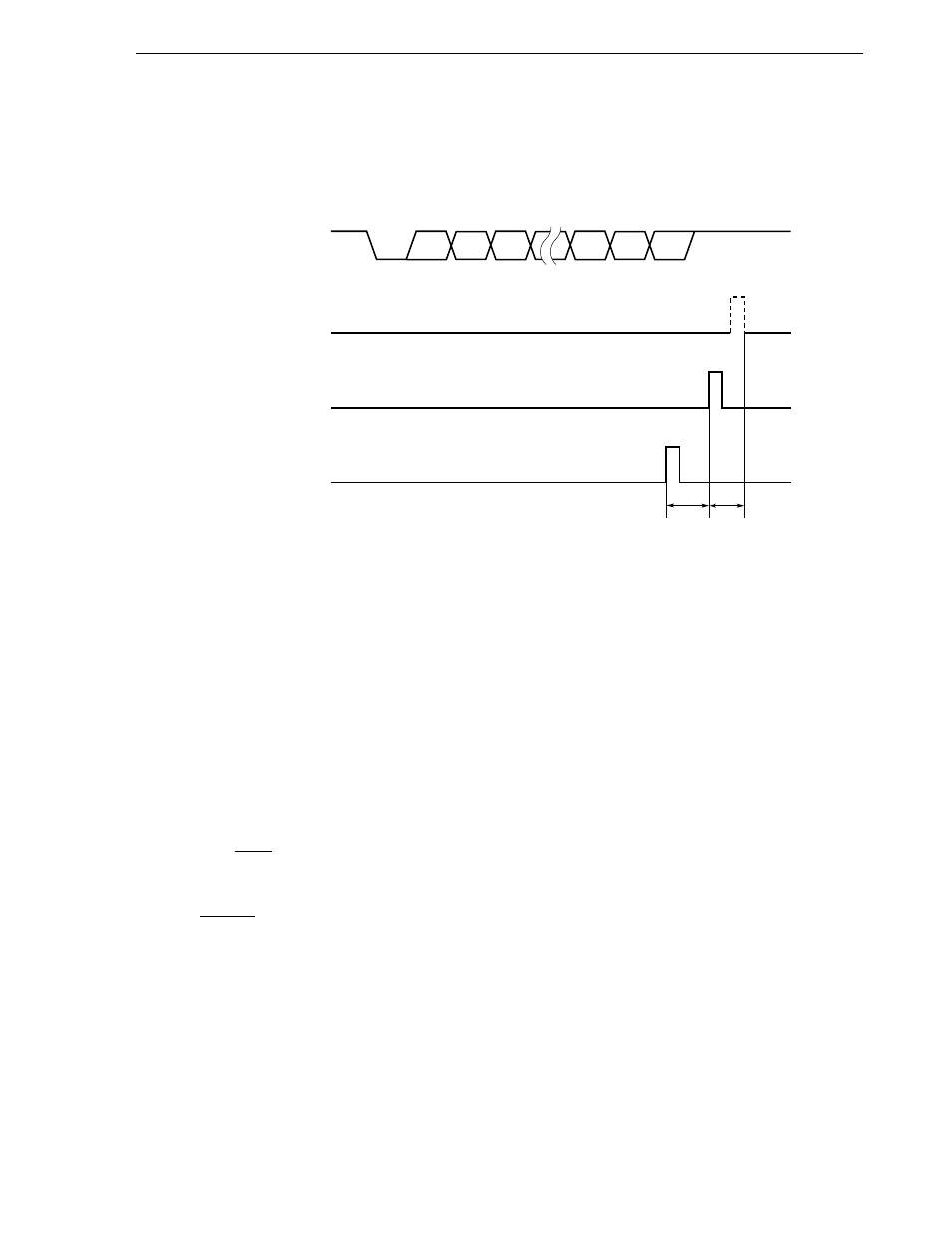

Disable the receive buffer register (RXB) from being read for a certain time (T1 + T2 in Figure 19-15) after

the reception error interrupt request (INTSER) has occurred.

Figure 19-15. Receive Buffer Register Read Disable Period

T1 : Time of one data of baud rate selected by baud rate generator control register (BRGC) (1/baud rate)

T2 : Time of 2 clocks of source clock (f

SCK

) of 5-bit counter selected by BRGC

•

Example of preventive measures

Here is an example of the above preventive measures.

[Condition]

f

X

= 5.0 MHz

Processor clock control register (PCC) = 00H

Oscillation mode select register (OSMS) = 01H

Baud rate generator control register (BRGC) = B0H (2400 bps selected as baud rate)

T

CY

= 0.4

µ

s (t

CY

= 0.2

µ

s)

T1 =

1

= 416.7

µ

s

2400

T2 = 12.8

×

2 = 25.6

µ

s

T1 + T2

= 2212 (clocks)

t

CY

D0

D1

D2

D6

D7

Parity

START

STOP

T1

T2

RxD (input)

INTSR

INTSER (on occurrence of

framing/overrun error)

INTSER (on occurrence of

parity error)